對FPGA設計而言如果想速度更快則應當努力減少路徑上LUT的個數,而不是邏輯級數。如果想面積更小則應當努力減少LUT的個數而不是邏輯門數。

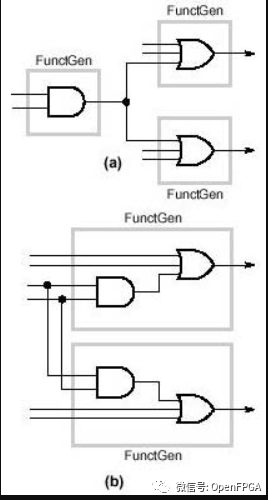

如下圖:

采用圖a結構,我們知道一個LUT只有一個輸出,因此前面的2輸入與門要占用一個LUT 后面的2個三輸入或門要各占用一個LUT 總共占用3個LUT LUT級數是2級。

采用圖b結構,其實現結果等效于圖a結構,雖然增加了一個2輸入與門并且邏輯級數與圖a一樣也是2級但我們根據LUT特點它只占用2個LUT:

2輸入與門和3輸入或門由一個LUT實現LUT級數只有1級,這就是一個門數增加邏輯級數未變但資源占用減少速度更快典型案例

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA設計

+關注

關注

9文章

431瀏覽量

28184 -

LUT

+關注

關注

0文章

52瀏覽量

13169

原文標題:【FPGA】減少路徑上的LUT個數使速度更快

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

CyU3PDmaMultiChannelCommitBuffer失敗后,如何使重置速度更快?

1) CyU3PDmaMultiChannelCommitBuffer 失敗后,如何使重置速度更快?

2) 如何將微控制器其他部分的內存用于幀緩沖?

發表于 07-23 08:29

LUT實現的逆變器真的是FPGA上的逆變器嗎?

你好,當我在原理圖視圖中單擊LUT時,它會按預期顯示逆變器。但我想知道它是通過逆變器在Xilinx FPGA上實現還是實際上原理圖不等同于FPGA的真相?謝謝,?以上來自于谷歌翻譯以下為原文Hi

發表于 01-29 09:22

Spartan 3器件上的專用乘法器路徑時間隨著階段數量的增加而減少

到的塊的數據表包含與乘法速度和流水線級數量相關的表格。 )。我在18x18bit乘法器上使用17x17bit信號進行了一些測試,以查看流水線級和速度之間的關系,以找到我設計的最佳級數。結果很奇怪。在

發表于 06-13 15:56

如何讓這個設計通過減少顏色量可能更快

/psoc-4-pioneer-kit-community-project060-psoc-4-mini-billboard我想讓這個設計通過減少顏色量可能更快。有人對此有經驗嗎?如何做到這一點呢? 以上來自于百度翻譯 以下為

發表于 07-23 10:07

Kintex 7輸入IO焊盤和FF(片寄存器)之間的額外LUT是什么

在Kintex 7目標(我正在使用xc7k410t)上,在P& R之后,我發現ISE在輸入焊盤和切片寄存器之間的每個數據網上放置了3個額外的LUT,充當路徑引線。但是在設備利用

發表于 07-16 07:26

怎樣去解決NVIC_EnableIRQ使能無法進行的問題呢

NVIC_EnableIRQ使能無法進行這是為什么呢?怎樣去解決NVIC_EnableIRQ使能無法進行的問題呢?

發表于 01-18 06:21

求助前輩們Verilog lut個數的問題

問一下這幾個模塊有幾個lut,因為是新手,不知道綜合出哪些函數,需要講函數來源細一些。然后是延遲上有什么,多少級lut。注:最后兩張圖片有示例調用。

發表于 12-13 14:03

如何使FRAM MCU速度更快所需功耗最低

、9uA就可以把數據寫完。通過比較可以看到,如果要寫很多數據到Flash等傳統存儲器里,FRAM速度會更快而所需功耗卻最低。從擦寫數據次數來看,一般存儲器寫一萬來次就到了極限,可FRAM可以在寫了10次方后仍可繼續進行擦寫操作。由于FRAM

發表于 11-16 10:21

?8次下載

怎樣減少路徑上的LUT個數使速度更快呢?

怎樣減少路徑上的LUT個數使速度更快呢?

評論