電子發(fā)燒友網(wǎng)報道(文/李彎彎)近幾年,汽車電動化、智能化迅速發(fā)展,這使得汽車上使用的芯片數(shù)量越來越多、金額越來越大。每輛車上用到的芯片數(shù)量幾乎翻倍,一些高端車型使用的芯片數(shù)量甚至超過1000顆,每輛車上所使用的金額比重也大幅提升。

然而,車規(guī)時代基本追求零質(zhì)量缺陷目標,車規(guī)產(chǎn)品全流程都要進行嚴格的質(zhì)量把控,不同環(huán)節(jié)都有不同的質(zhì)量管理標準,如AECQ100、IATF 16949、ISO26262等。對于企業(yè)來說,如何低成本設(shè)計、生產(chǎn)出高質(zhì)量的車規(guī)產(chǎn)品,離不開高效測試解決方案的強力助攻。

質(zhì)量問題帶來的各種顯、隱性成本

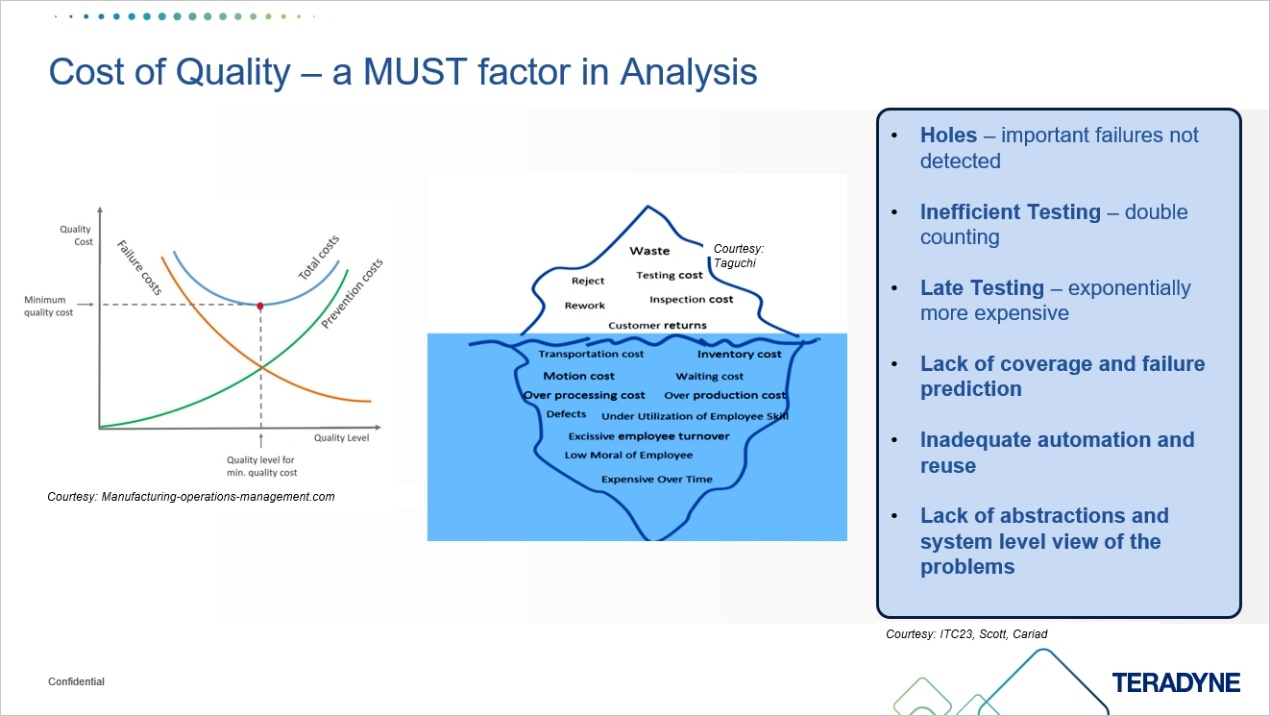

“質(zhì)量問題,會帶來各種顯性或隱性成本。”在日前的泰瑞達年度媒體見面會上,該公司中國區(qū)總經(jīng)理Felix Huang先生向媒體表示。如下圖所示,最左側(cè)橫坐標是質(zhì)量等級,縱坐標是質(zhì)量帶來的成本。可以看到,紅色這條線表示,質(zhì)量等級越高,后面器件帶來失效的成本就會降低;綠色這條線表示,為了追求質(zhì)量要做一些預(yù)防性的提前檢測,因此為了追求高質(zhì)量,額外會帶來成本的增加。實際上,每家企業(yè)都會考慮成本和質(zhì)量的平衡點。

Felix Huang先生解釋說:“雖然都是裝在車上,不同芯片的質(zhì)量和成本要求不一樣。比如,用在自動駕駛和智能座艙上的主控芯片,它們的質(zhì)量要求必然不同,自動駕駛對質(zhì)量要求更高,因為涉及到安全性的問題。其他的還有MCU、傳感器等質(zhì)量要求也會有區(qū)別。”

如上圖中間的冰山圖,海平面之上是能夠看到的顯性的成本,如質(zhì)量問題帶來的客退、測試成本;海平面之下是一些隱性成本,如果質(zhì)量控制不好會帶來很多成本,如庫存成本、運輸成本,再往下甚至會引起人員變動帶來的成本。Felix Huang先生認為,隱形帶來的成本對社會的影響遠遠超過顯性成本。

此外,如果測試方案不好,也會到來很多問題,比如:有一些失效問題沒辦法檢測出來;由于測試方案不好,需要多次測試,增加測試工序;有些問題在前面就應(yīng)該識別,結(jié)果到后面才識別出來,從而增加生產(chǎn)和裝配成本等。在Felix Huang先生看來,在產(chǎn)品設(shè)計的初期就應(yīng)該考慮好測試的設(shè)計和策略,這樣才能有效避免上述問題。

如何達成車規(guī)要求的零質(zhì)量缺陷目標

如何才能達成車規(guī)要求的零質(zhì)量缺陷目標呢?Felix Huang先生認為,首先是要考慮測試策略,即在開始設(shè)計芯片的時候,就要想要達到0 DPPM的效果,在設(shè)計階段到最終量產(chǎn)階段每個環(huán)節(jié)是怎樣的,如何去保證質(zhì)量;其次是流程怎么做,即在實現(xiàn)這個流程的過程中,如何進行多步驟協(xié)作、多人協(xié)作,如何做到盡可能自動化,減少人為因素帶來的問題;最后是需要什么樣的工具來支撐,是否有可靠的工具能夠做實時性、可預(yù)測性、智能性分析。

具體來看,在測試策略方面,需要有一個比較靈活的測試流程來盡量優(yōu)化質(zhì)量成本。在完成芯片的過程中有多個檢測階段:1、Wafer Sort(晶圓測試),也就是在晶圓階段通過測試機檢測有沒有壞的Die;2、Partial Assembly,最終芯片會裝配在PCB板上,這個階段要對PCB板裝配進行檢測;3、Final Test(成品測試),即在芯片完成之后切割Die,之后進行封裝,對封裝也需要做檢測;4、System Level Test,這個是把芯片安裝到最終應(yīng)用的系統(tǒng)板上,需要做一個系統(tǒng)級測試。針對上述每個階段的測試,泰瑞達都有不同的機臺可以覆蓋。

泰瑞達能提供較靈活的測試策略(FLEX TEST)。從上圖可以看到,兩側(cè)都有箭頭,也就是說測試的側(cè)重點可以左移,也可以右移。什么意思呢?很多芯片上的缺陷都希望能夠盡早發(fā)現(xiàn),如果很多問題在晶圓測試階段就能夠檢測出來,到了成品測試時就不需要再去檢測,只需要去檢測封裝時Die與Die之間互連可能帶來的問題。

對于一顆芯片來說,其測試成本相較于工藝、封裝占比較小,將測試項更多的移到前面,越早發(fā)現(xiàn)問題,就可以省去后面封裝帶來的成本。從成本的角度來看,可以考慮檢測是不是能夠往前移一點。當然有些不能移的,就只能在后面添加上去。

要實現(xiàn)這樣一個FLEX測試,對測試的要求其實很高,首先是要求它的機臺本身要求非常好的穩(wěn)定性、可重復(fù)性;其次是要求其測試能力和覆蓋率要達到要求。

測試流程方面,它并不像表面看上去那么簡單,不僅僅是篩出芯片的好和壞。它需要不斷分析數(shù)據(jù),分析完數(shù)據(jù)后,才能確定哪些項目要往移。這里面需要非常多的技術(shù)和工具支撐。Felix Huang先生介紹說:“泰瑞達內(nèi)部有一個專門的軟件工具PortBridge,早期IC設(shè)計人員和ATE測試人員很難溝通,PortBridge起到了一個溝通橋梁的作用。EDA的設(shè)計人員、DFT人員可以通過Mentor Graphics的理念,用EDA工具直接連接我們的測試機直接驗證設(shè)計向量。”

PortBridge這個軟件裝集成在IG-XL開發(fā)環(huán)境里面,通過EDA工具訪問測試機控制晶圓測試、成品測試和SLT,根據(jù)它們的結(jié)果實時在線做調(diào)試。這使得在設(shè)計階段就可以直接看ATE的測試結(jié)果,并反饋給Fab,其作用主要是在早期階段有助于調(diào)試良率。

此外,在ATE開發(fā)測試程序上,泰瑞達也探索出了高效的方法和工具。從1995年到2020年,測試程序復(fù)雜度越來越大。最早測試一顆SoC混合芯片可能只有200個測試項,代碼量大概一兩千行,現(xiàn)在芯片要測試更加復(fù)雜的功能及不同的場景,代碼量大概到了2萬行。以前這個階段一個或幾個工程師就能基本完成,如今不僅僅是芯片復(fù)雜度增加,開發(fā)周期也要求越短越好,基本上都需要多人開發(fā),開發(fā)測試程序基本都是一個團隊。Felix Huang先生告訴媒體:“因為需要協(xié)同不同地方的人開發(fā),最后再整理調(diào)試,這對一些工具、自動化、智能化提出了要求。在這方面,我們有多人協(xié)同分布式處理開發(fā)工具Git,以自動把版本做合并。此外,還有一些不同的工具寫成腳本,也有在過程中不斷優(yōu)化的工具。”

可以看到,測試的整個測試流程相當復(fù)雜的,從第一階段開始跟芯片設(shè)計師談早期的測試方案;第二階段測試程序的設(shè)計,包括代碼、調(diào)試等;到第三階段把每個工程師調(diào)的不同流程整合構(gòu)建在一起,形成一個完整的解決方案;第四階段對代碼做標準化,拿掉冗余的部分等;最終得到質(zhì)量達標、成本低、又好用的方案發(fā)布生產(chǎn)。

在工具方面,首先是IG-XL軟件,是ATE行業(yè)中用戶最廣,評價最高同開發(fā)軟件,其實用性、易用性和穩(wěn)定性都處于業(yè)界領(lǐng)先水平。泰瑞達所有的Soc測試設(shè)備都采用這個開發(fā)環(huán)境,便于用戶開發(fā)。

其次是Oasis,它是基于IG-XL軟件的一個輔助工具,可以檢測開發(fā)的代碼質(zhì)量,比如,在Offline階段運行Oasis工具,可以自動看不同工程師寫出來的代碼有沒有錯、有沒有冗余。

還有一款全流程管理軟件DevOps,這是一款完全自動化的全流程管理軟件,基于IG-XL開發(fā)軟件和Oasis輔助軟件來保證代碼調(diào)試過程的質(zhì)量。工程師開始開發(fā)一個測試程序的時候,從Offline階段就會自動調(diào)用Oasis中的Offline檢測工具,生成一個報告,將問題發(fā)到相關(guān)工程師的郵箱,直到把報告中的的問題全部修復(fù)以后才會進入到下一個階段。

另外,F(xiàn)elix Huang先生重點談到公司的一款數(shù)據(jù)分析工具UltraEDGE。在整個見面會上,F(xiàn)elix Huang先生多次強調(diào)數(shù)據(jù),整個流程從前到后流動的就是大數(shù)據(jù),海量的數(shù)據(jù)支撐來達到0 DPPM。這款工具可以在前面的測試結(jié)果出來之后,進行數(shù)據(jù)分析和反饋。

UltraEDGE具體如何工作呢?如上圖,晶圓從中間刻蝕機出來之后上右側(cè)的ATE測試機。晶圓測試完成后,大量數(shù)據(jù)進入UltraEDGE,在里面可以自建一些FDE Fault Detect Engine工具,進行質(zhì)量和數(shù)據(jù)統(tǒng)計;也可以在上面安裝第三方數(shù)據(jù)分析軟件,比如OptimalPlus、PDF數(shù)據(jù)管理軟件,在其中進行加密和機器學習,對抓取到的原始數(shù)據(jù)進行分析。之后形成晶圓圖,在晶圓上的多個Die中,綠色表示通過,紅色表示失效,藍色表示可能有一些是邊緣性的問題。把一些潛在的缺陷問題體現(xiàn)出來,反饋給Foundry,從而進行工藝的調(diào)整和改善。UltraEDGE最終目的是提升良率,降低成本。

總結(jié)

如今汽車電動化、智能化是未來趨勢,車規(guī)芯片的市場需求將會越來越大。同時車規(guī)芯片對質(zhì)量的要求也更高。對于芯片企業(yè)來說,選擇合適的測試方案,有助于企業(yè)以更低成本打造出高質(zhì)量的產(chǎn)品,并能夠以更快速的時間實現(xiàn)上市。泰瑞達擁有全覆蓋的測試機臺,能夠針對不同企業(yè)不同芯片設(shè)計合適的測試策略,同時它也創(chuàng)新性研發(fā)出各種工具,使得測試的各個環(huán)節(jié)更加高效,真正助力芯片企業(yè)達成高質(zhì)量低成本目標。

-

測試

+關(guān)注

關(guān)注

9文章

6203瀏覽量

131375 -

泰瑞達

+關(guān)注

關(guān)注

1文章

20瀏覽量

8511 -

車規(guī)芯片

+關(guān)注

關(guān)注

0文章

245瀏覽量

8086

發(fā)布評論請先 登錄

大會演講回顧– 愛德萬 泰瑞達 | AI 賦能半導(dǎo)體測試,兩大實戰(zhàn)案例解鎖測試優(yōu)化新路徑

車規(guī)級單通道低邊驅(qū)動器SiLM27531M,助力GaN/SiC功率系統(tǒng)高效運行

汽車軟件質(zhì)量躍遷的系統(tǒng)性路徑:基于ISO 26262標準的單元測試體系重構(gòu)與中日實踐深度對比(2026學術(shù)研究報告)

車規(guī)級與消費級芯片的差異與影響

格創(chuàng)東智QMS解決方案助力封測企業(yè)實現(xiàn)從檢驗到預(yù)防的質(zhì)量躍遷

車規(guī)級電子元器件AEC-Q100認證測試

卡倫測控:車規(guī)級電子元器件AEC-Q認證測試

車規(guī)級和消費級有什么區(qū)別?為什么自動駕駛需要車規(guī)級?

RISC-V車規(guī)芯片加速 芯來NA900汽車電子客戶矽力杰與普華達成戰(zhàn)略合作

康謀分享| 揭秘C-NCAP :合成數(shù)據(jù)如何助力攻克全球安全合規(guī)難關(guān)?

【新聞】車規(guī)平臺硬實力哪家強?

中美貿(mào)易摩擦背景下國家車規(guī)芯片產(chǎn)業(yè)應(yīng)對策略

泰矽微車規(guī)觸控芯片產(chǎn)品介紹

車規(guī)芯片AEC-Q100認證的關(guān)鍵測試解析

車規(guī)級與非車規(guī)級有什么區(qū)別?如何管控?

泰瑞達創(chuàng)新測試策略,助力車規(guī)芯片實現(xiàn)零質(zhì)量缺陷目標

泰瑞達創(chuàng)新測試策略,助力車規(guī)芯片實現(xiàn)零質(zhì)量缺陷目標

評論