這次講的還是上次說的那篇文章,把除了PSR的其他指標(biāo)分析總結(jié)一下:

1. load regulation

首先看一下load regulation。這個(gè)指標(biāo)是為了衡量regulator的負(fù)載電流變化會(huì)引起多少輸出電壓的變化,也就是?Vout/?iL。從公式容易看出,這表征著regulator的輸出阻抗,而這個(gè)值越小越好。

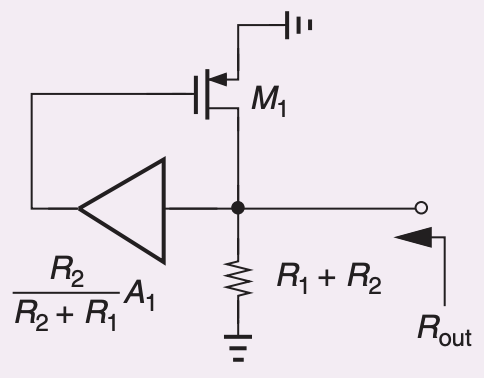

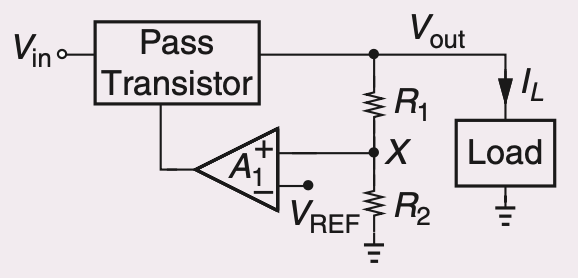

圖一

1.1 PMOS型regulator

對(duì)于PMOS型的regulator,也就是我們常說的LDO,可按圖一進(jìn)行計(jì)算。和PSR的計(jì)算類似,將電阻串分壓比乘到運(yùn)放的增益上,那么輸出節(jié)點(diǎn)往上看就是一個(gè)gm-boosted diode-connected PMOS,此時(shí)的跨導(dǎo)表示為

那么整個(gè)regulator的輸出阻抗就可以寫為

考慮到并聯(lián)的第一項(xiàng)遠(yuǎn)小于第二項(xiàng),可以忽略第二項(xiàng),重新表示為

為了得到更好的load regulation,運(yùn)放的增益越大越好。 這與PSR改善的思路是保持一致的。

隨著頻率升高到運(yùn)放主極點(diǎn)ω0之后,輸出阻抗開始增大,如圖二。

圖二

此時(shí)的輸出阻抗Zout可以表示為

和PSR的分析相同,設(shè)計(jì)一個(gè)高增益,大帶寬的運(yùn)放也是有助于改善load regulation的。除此之外,在輸出節(jié)點(diǎn)加一個(gè)對(duì)地的大電容CM,1/(s*CM)和上述的Zout并聯(lián)在一起,當(dāng)頻率較高時(shí),電容的阻抗減小,也可以緩解圖二中高頻下Zout的上升。并聯(lián)電容后的曲線如圖三。

圖三

圖三能看出在ω0之后阻抗仍有一個(gè)上升的尖峰。為了避免這個(gè)問題,設(shè)計(jì)時(shí)希望1/(ω0*CM)盡可能接近低頻下的|Zout|。但由于這個(gè)值本身非常小,CM可能會(huì)高達(dá)幾十nF。這在片上顯然是難以實(shí)現(xiàn)的。同時(shí),這引入了另一個(gè)問題,CM越大,regulator輸出節(jié)點(diǎn)的極點(diǎn)頻率越低,和運(yùn)放輸出的極點(diǎn)可能會(huì)很接近,引起穩(wěn)定性的問題。

1.2 NMOS型regulator

圖四

如圖四,忽略M1的rout和負(fù)載電阻的情況下,Rout可簡(jiǎn)單表示為1/gm除以1加環(huán)路增益:

分母第二項(xiàng)遠(yuǎn)大于1,再次整理公式:

對(duì)比可以發(fā)現(xiàn),這和PMOS型的regulator是一模一樣的。也就是說,從load regulation的角度來講,兩者無性能上的差異。

但和前面不同的是,如果通過在輸出對(duì)地接大電容CM來改善高頻下的PSR和load regulation,輸出極點(diǎn)近似表達(dá)為1/((1/gm)*CM),由于1/gm較小,其輸出極點(diǎn)是遠(yuǎn)高于PMOS型regulator的輸出極點(diǎn)的,那么此時(shí)的穩(wěn)定性就更有可能得到保證。除此之外,M1的CGS此時(shí)跨接在運(yùn)放輸出和regulator輸出兩個(gè)節(jié)點(diǎn)之間,通過密勒定理等效到運(yùn)放輸出的電容可能比實(shí)際的CGS更小,那么regulator的帶寬就有希望做得更高。也就是說,對(duì)于NMOS型regulator,或許可以先在輸出對(duì)地加大電容CM來保證load regulation,再去完成穩(wěn)定性補(bǔ)償。

2. noise

圖五

如圖五,以PMOS型regulator為例,將運(yùn)放噪聲等效到輸入,M1的噪聲等效到柵極,再想辦法推導(dǎo)到輸出。M1柵極的噪聲可以除以運(yùn)放增益同樣等效到運(yùn)放輸入端,再將總的噪聲除以電阻串分壓比,就可以計(jì)算到輸出:

可以看出, 對(duì)于M1貢獻(xiàn)的噪聲,運(yùn)放增益越大,抑制得越好 。另外,電阻串和bangap reference也是噪聲源,熱噪聲4kT(R1||R2)和Vref本身的噪聲都可以簡(jiǎn)單地疊加到運(yùn)放輸入端進(jìn)行計(jì)算。

和前面一樣,隨著運(yùn)放高頻增益降低,輸出端噪聲影響會(huì)更顯著。因此,保持運(yùn)放高增益的情況下增大其帶寬對(duì)噪聲抑制也有好處。

事實(shí)上,換成NMOS型regulator,噪聲的分析也是一樣的,所以二者在噪聲性能上無差異。

3. 總結(jié)

通過這兩篇文章的分析和對(duì)比,可以總結(jié)一下用PMOS和NMOS做pass device的regulator的異同,給大家設(shè)計(jì)提供參考:

同: load regulation和noise性能無差異;都可以通過提高運(yùn)放的增益和帶寬來改善PSR/load regulation/noise

異: NMOS型regulator的PSR遠(yuǎn)好于PMOS型regulator;NMOS型regulator更有希望實(shí)現(xiàn)高帶寬;NMOS型regulator更有希望通過增加輸出大電容改善PSR和load regulation,同時(shí)不影響穩(wěn)定性

(當(dāng)然,NMOS型regulator就不能實(shí)現(xiàn)low dropout了)

-

負(fù)載電流

+關(guān)注

關(guān)注

1文章

629瀏覽量

15221 -

ldo

+關(guān)注

關(guān)注

35文章

2442瀏覽量

159955 -

運(yùn)放

+關(guān)注

關(guān)注

49文章

1229瀏覽量

55604 -

PMOS

+關(guān)注

關(guān)注

4文章

271瀏覽量

31609 -

輸出阻抗

+關(guān)注

關(guān)注

1文章

104瀏覽量

12755

發(fā)布評(píng)論請(qǐng)先 登錄

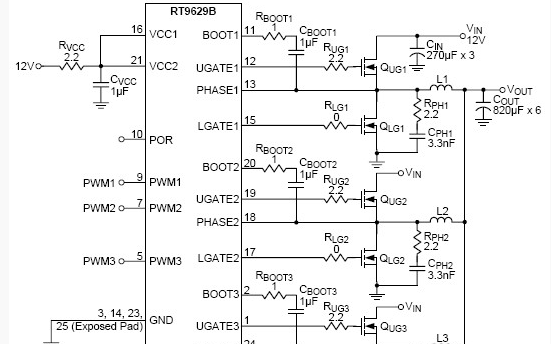

如何分析這個(gè)電路及主芯片關(guān)鍵參數(shù)指標(biāo)?

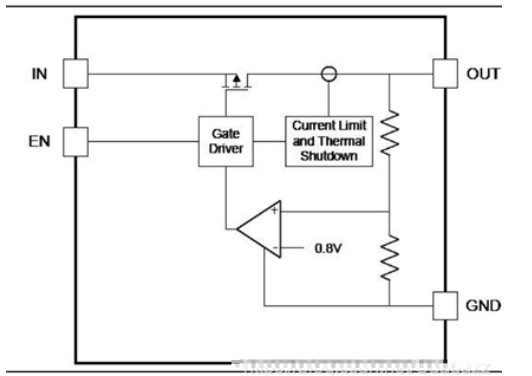

LDO簡(jiǎn)介、工作原理及性能指標(biāo)

詳解LDO的幾個(gè)重要參數(shù)

LDO的參數(shù)指標(biāo)分析(1)

LDO關(guān)鍵的指標(biāo)和定義,您了解嗎?

LDO的基本原理與主要參數(shù)

設(shè)計(jì)LDO電源需要注意的事項(xiàng)

選擇一款LDO要關(guān)注哪些指標(biāo)

使用LDO必須掌握的重要參數(shù)

以TI的LM2941--1A LDO穩(wěn)壓器為例講解LDO電路的設(shè)計(jì)

同軸電纜的參數(shù)指標(biāo)

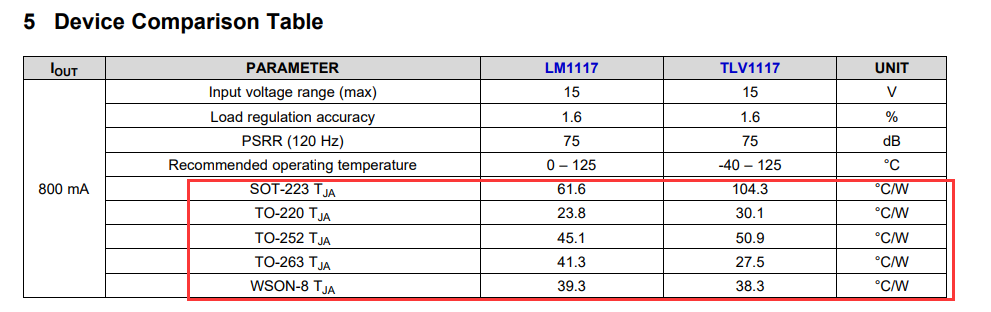

LDO參數(shù)解讀、特性、參考設(shè)計(jì)

LDO的參數(shù)指標(biāo)分析(2)

LDO的參數(shù)指標(biāo)分析(2)

評(píng)論