在刻蝕SOI襯底時,通常會發生一種凹槽效應,導致刻蝕的形貌與預想的有很大出入。那么什么是凹槽效應?什么原因引起的?怎么抑制這種異常效應呢?

什么是凹槽效應?

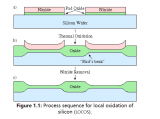

凹槽效應,英文名稱notching effect,又可以叫做缺口效應。指的是在多層結構的干法刻蝕過程中,會在某一層的邊緣形成不希望出現的凹槽,影響整個芯片的性能。"Notching Effect" 并不是SOI襯底的專屬,它是一個廣泛存在于多層材料刻蝕過程中的現象。本文以SOI襯度刻蝕為例,來解釋這一現象。

SOI襯底的中間有一層氧化硅,上下均為硅單晶。理論上,干法刻蝕過程在遇到氧化硅層時應當自動停止,即氧化硅作為一個刻蝕終止層。

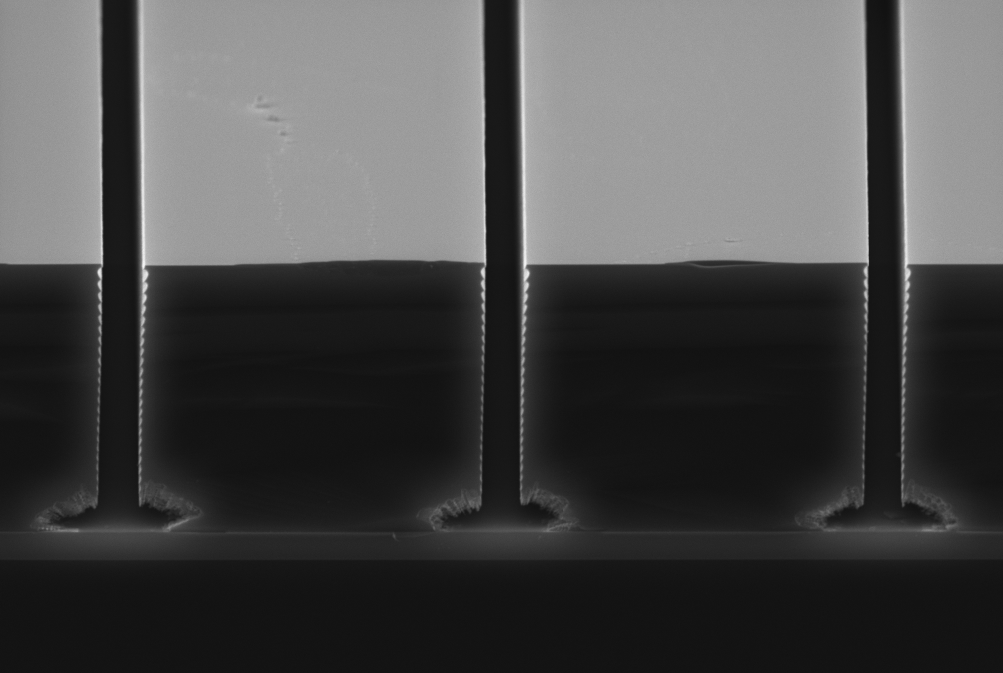

但是,實際過程中,在刻蝕到二氧化硅層后,刻蝕并沒有完全停止。刻蝕在二氧化硅層的表面繼續進行,形成橫向的刻蝕,造成了凹槽效應。

凹槽效應的形成機理

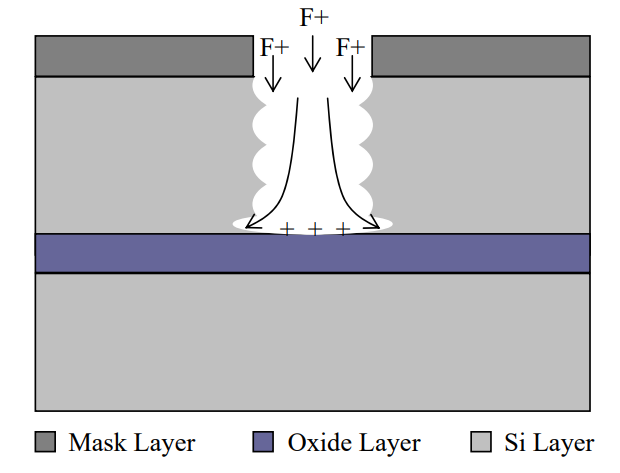

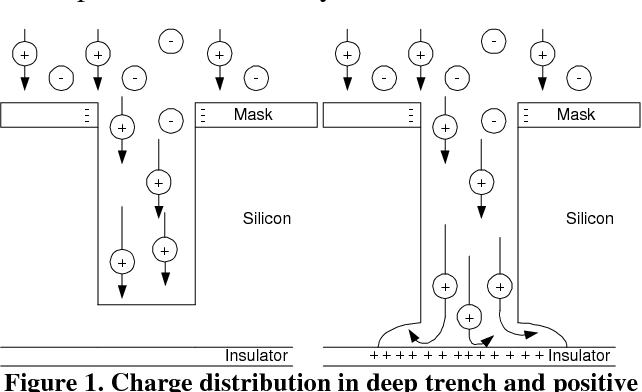

由于氧化硅層本身的絕緣特性,離子電荷會在氧化硅上大量積聚。在氧化硅層表面積累的正電荷形成一個局部電場。

這個電場會改變進入材料的離子軌跡,使其沿著硅氧化層的表面橫向刻蝕,在多層材料的交界處,由于離子的橫向刻蝕,形成一個不期望的缺口。 ?

?

如何減弱凹槽效應?

上面我們已經了解到凹槽效應主要來源于絕緣層電荷的積累,那么我們抑制凹槽效應的一大思路便是及時導散掉積累的電荷,不讓氧化硅表面有過多的電荷聚集。圍繞著這個思路,我們可以從以下幾個當面入手:

1,設計時做好考慮

在設計階段就需要考慮到凹槽效應的可能性,預留出相應空間,避免高深寬比的結構,防止負載效應加深凹槽效應。

2,優化工藝參數.

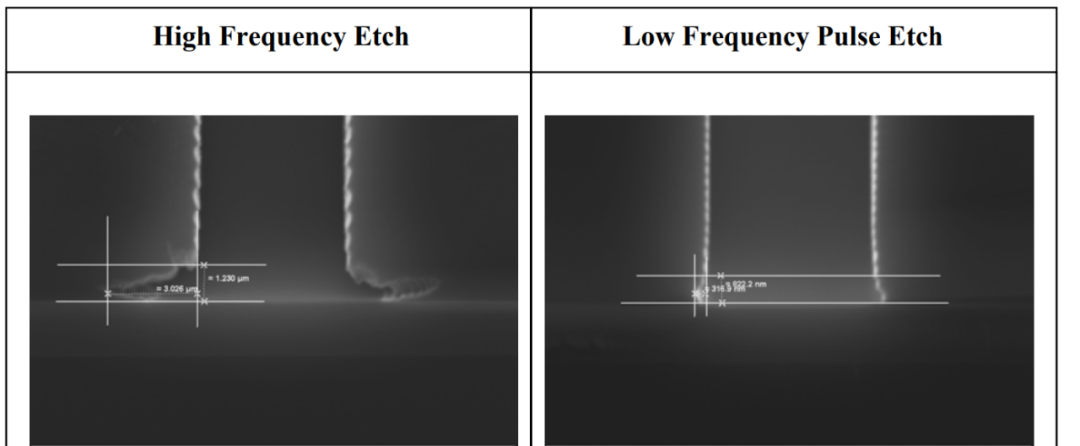

通過改變刻蝕參數(電源頻率、刻蝕氣體種類和流量等)來找到一個更優化的刻蝕條件,以減輕凹槽效應。

例如,在其他條件不變的情況下,采用低頻率產生的凹槽效應就遠遠小于高頻率產生的凹槽效應。如下圖:

3,分步刻蝕

在剛開始階段,使用高刻蝕速率的參數來移除大部分材料。

當刻蝕接近目標層時,減小刻蝕速率、減小RF功率或增加保護氣體的流量,以減小Notching Effect。

分步刻蝕適合優化在單一參數設置下可能出現的問題,有利于解決復雜結構中的刻蝕問題。

審核編輯:劉清

-

單晶硅

+關注

關注

7文章

194瀏覽量

29314

原文標題:什么是干法刻蝕的凹槽效應?

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

示波器探頭的負載效應介紹

PWM停止輸出,什么原因會導致這種現象發生?

LOCOS工藝中鳥喙效應的形成原因和解決措施

碳化硅襯底 TTV 厚度測量中邊緣效應的抑制方法研究

晶圓切割中深度補償 - 切削熱耦合效應對 TTV 均勻性的影響及抑制

晶圓切割中振動 - 應力耦合效應對厚度均勻性的影響及抑制方法

什么是凹槽效應?什么原因引起的?怎么抑制這種異常效應呢?

什么是凹槽效應?什么原因引起的?怎么抑制這種異常效應呢?

評論