什么是同步有限狀態機?

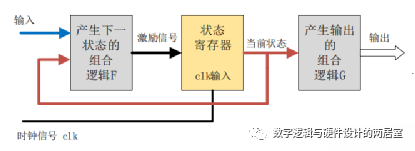

同步:所有的狀態跳轉都是在時鐘的作用下進行

有限:狀態的個數是有限的

為什么要用狀態機?

FPGA是并行處理的,如果我們想要處理具有前后順序的事件時,就需要引入狀態機。狀態機的每一個狀態代表一個事件,從執行當前事件到執行另一事件我們稱之為狀態的跳轉或狀態的轉移。

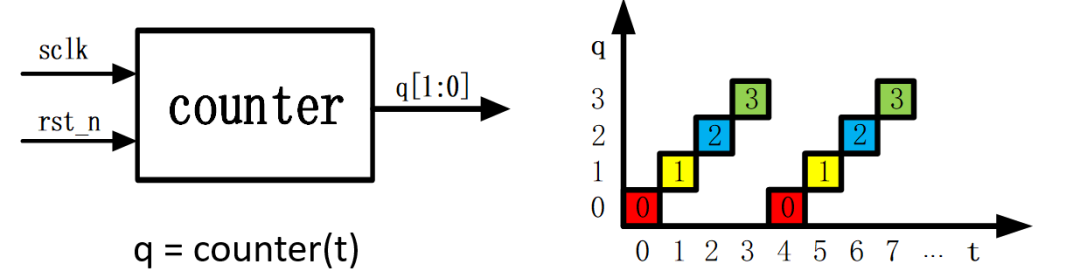

狀態機特別適合描述那些發生有先后順序或時序規律的事情。小到計數器大到微處理器都適合用狀態機描述。

怎么表示狀態機?

狀態機需要具備什么?

- 輸入:根據輸入確定是否需要進行狀態跳轉

- 輸出:當前時刻狀態要做的事情是什么

- 狀態:要處理的事情

狀態機的設計步驟是怎么樣的?

- 首先分析輸入、輸出有哪些,需要多少個狀態

- 其次根據分析繪制狀態轉移圖

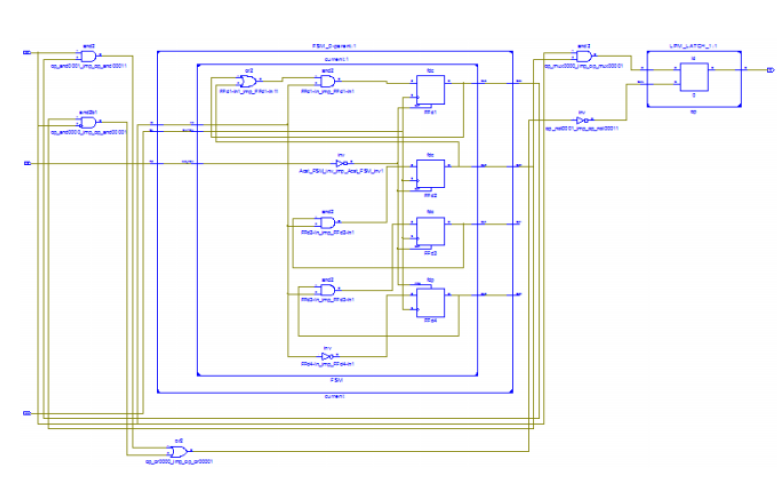

- 設計實現的模塊

- 狀態機代碼的編寫

FIFO的使用

什么是FIFO?

FIFO(First In First Out)即先入先出,是一種數據緩沖器,用來實現數據先入先出的讀/寫方式。FIFO有一個寫端口和一個讀端口外部無需使用者控制地址,使用方便。

根據FIFO工作的時鐘域可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。異步FIFO是指讀/寫時鐘不一致,是相互獨立的。

FIFO的作用是什么?

- 用于緩存數據

- 用于做多bit數據的跨時鐘域處理

- 用于做時鐘、位寬不匹配問題的接口

如何使用FIFO?

- 在一定時間內,寫數據的總帶寬一定要小于等于讀數據的總帶寬

- 控制好FIFO的關鍵信號,讀寫時鐘、讀寫使能、空滿標志信號

- FIFO一定不能寫滿、也不能讀空,要考慮FIFO的背靠背問題,設置好存儲深度

FPGA設計中的技巧

一、使能信號(en)、標志信號(flag)、計數器(cnt)

二、模塊框圖設計——方案的確定

三、波形設計——代碼的實現

四、代碼規范——可復用性和效率

五、仿真調試——修改查錯

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA設計

+關注

關注

9文章

431瀏覽量

28151 -

有限狀態機

+關注

關注

0文章

52瀏覽量

10683 -

狀態機

+關注

關注

2文章

499瀏覽量

29171 -

FIFO存儲

+關注

關注

0文章

103瀏覽量

6320 -

數據緩沖器

+關注

關注

1文章

11瀏覽量

1938

發布評論請先 登錄

相關推薦

熱點推薦

什么是有限狀態機呢

在嵌入式,機器人領域,由于多的復雜邏輯狀態,我們編寫程序的時候不得不考慮很多種情況,容易造成功能間的沖突。有限狀態機(finite-state machine),簡稱狀態機,是一種表示

發表于 12-20 06:51

有限狀態機的建模與優化設計

本文提出一種優秀 、高效的 Verilog HDL 描述方式來進行有限狀態機設計 介紹了 有限狀態機的建模原則 并通過一個可綜合的實例 驗證了 該方法設計的有限狀態機在面積和功耗上的優勢。

發表于 03-22 15:19

?1次下載

VHDL有限狀態機設計-ST

EDA的有限狀態機,廣義而言是指只要涉及觸發器的電路,無論電路大小都可以歸結為狀態機。有限狀態機設計在學習EDA時是很重要的一章。

發表于 06-08 16:46

?3次下載

初學者對有限狀態機(FSM)的設計的認識

有限狀態機(FSM)是一種常見的電路,由時序電路和組合電路組成。設計有限狀態機的第一步是確定采用Moore狀態機還是采用Mealy狀態機。

發表于 02-11 13:51

?4760次閱讀

基于事件驅動的有限狀態機介紹

? 一、介紹 EFSM(event finite state machine,事件驅動型有限狀態機),是一個基于事件驅動的有限狀態機,主要應用于嵌入式設備的軟件系統中。 EFSM的設計原則是:簡單

基于事件驅動的有限狀態機介紹

EFSM(event finite state machine,事件驅動型有限狀態機),是一個基于事件驅動的有限狀態機,主要應用于嵌入式設備的軟件系統中。

什么是狀態機?狀態機的種類與實現

狀態機,又稱有限狀態機(Finite State Machine,FSM)或米利狀態機(Mealy Machine),是一種描述系統狀態變化的模型。在芯片設計中,

什么是同步有限狀態機?為什么要用狀態機?怎么表示狀態機?

什么是同步有限狀態機?為什么要用狀態機?怎么表示狀態機?

評論