相干集線器接口,俗稱 CHI,是一種接口規(guī)范,是5千從 Arm 生成 AMBA 協(xié)議 (AMBA?? 5),于 2013 年發(fā)布。AMBA? 5 CHI 定義了用于將完全相干處理器和動態(tài)內(nèi)存控制器連接到高性能無阻塞互連的接口。

AMBA CHI-E 建立在現(xiàn)有的 AMBA CHI-D(問題 D)規(guī)范之上(請參閱我們在 AMBA?? ?CHI-D 上的博客),引入了對以下各項的支持:一組新事務、獨占訪問功能、事務優(yōu)化、一系列性能吞吐量改進功能和關鍵的 Arm 架構功能。

一些新功能包括:

新交易和獨家交易

引入了新的請求事務類型,例如:ReadPreferUnique,MakeReadUnique,使用可選數(shù)據(jù)寫入,不帶數(shù)據(jù)的寫入零,兩部分存儲。此外,還引入了新的偵聽事務類型SnpPreferUnique,Snoop Query。

新增相干獨占訪問功能,提高獨占序列執(zhí)行效率。這些基于請求事務MakeReadUnique,ReadPreferUnique;Snoop transactions SnpPreferUnique 和 Snoop Query。

交易優(yōu)化功能

引入了新的事務流優(yōu)化,例如:直接寫入數(shù)據(jù)傳輸流、組合寫入和 CMO 事務、請求排序流優(yōu)化、將轉(zhuǎn)發(fā)監(jiān)聽視為請求節(jié)點的提示以及從請求節(jié)點到互連中的緩存的 SLC 替換提示傳播。

性能吞吐量改進功能

引入了關鍵的性能吞吐量改進功能,例如:給定組件的多個接口、單個接口上的復制通道、將事務 ID 寬度擴展到 12 位以及組 ID 字段的擴展。

協(xié)議架構特點

引入內(nèi)存標記擴展是為了符合 Arm v8.5 體系結構要求,這是一種可用于檢測內(nèi)存安全違規(guī)的機制。

引入了額外的 DVM 操作以與 Arm v8.4 架構保持一致。

您的系統(tǒng)在沒有壓力的情況下運行良好,這很好,但是當您高速運行并且有大量流量通過這些連貫網(wǎng)絡時會發(fā)生什么?在這里,Synopsys 提供了一個名為 VC VIP Auto Performance 的功能,它將按照 AMBA 自適應流量配置文件 (AMBA?? ATP) 生成流量。(您需要創(chuàng)建一個測試配置文件作為此工具的輸入。隨后,您可以在威爾第性能分析器中分析延遲和帶寬問題。

所有最新功能均在 AMBA 5 CHI 的 Synopsys 驗證 IP 中得到完全支持和提供。 適用于 AMBA?? 5 CHI 的 Synopsys 解決方案提供用于延遲和吞吐量分析的性能指標,以及針對協(xié)議、數(shù)據(jù)完整性和緩存一致性的全面系統(tǒng)級檢查。還包括內(nèi)置序列集合、功能覆蓋模型、驗證計劃和一組使用示例,以加快驗證覆蓋率的收斂速度。Synopsys VIP 與 Synopsys Verdi Protocol Analyzer 調(diào)試解決方案以及 Synopsys Verdi?? Performance Analyzer 原生集成。

審核編輯:郭婷

-

ARM

+關注

關注

135文章

9553瀏覽量

391881 -

控制器

+關注

關注

114文章

17791瀏覽量

193159 -

接口

+關注

關注

33文章

9520瀏覽量

157029

發(fā)布評論請先 登錄

如何解決數(shù)據(jù)庫與緩存一致性

Arm AMBA協(xié)議集AXI中,同時讀寫相同的address,數(shù)據(jù)的一致性怎么比較?

AMBA CHI協(xié)議介紹

CMP中Cache一致性協(xié)議的驗證

加速器一致性接口

Cache一致性協(xié)議優(yōu)化研究

自主駕駛系統(tǒng)將使用緩存一致性互連IP和非一致性互連IP

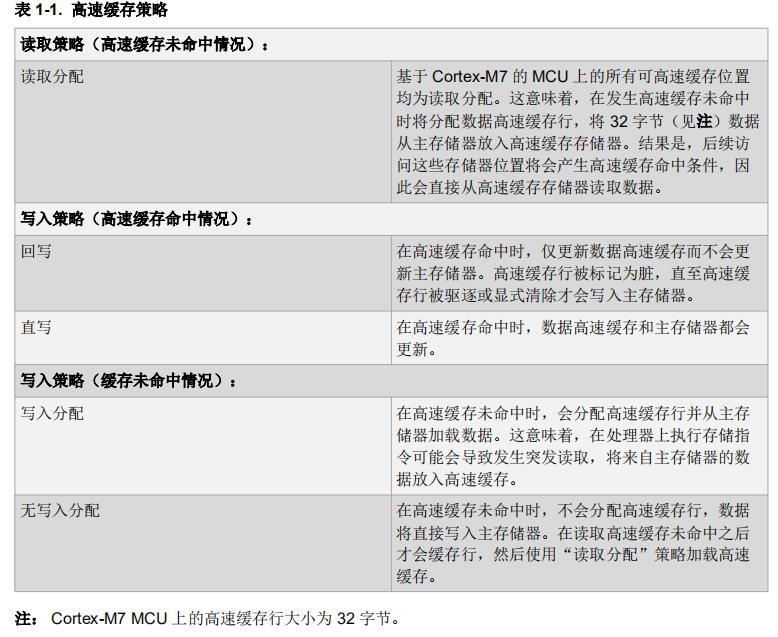

管理基于Cortex?-M7的MCU的高速緩存一致性

搞定緩存一致性驗證,多核SoC設計就成功了一半

本周五|搞定緩存一致性驗證,多核SoC設計就成功了一半

Redis緩存與Mysql如何保證一致性?

深入理解數(shù)據(jù)備份的關鍵原則:應用一致性與崩潰一致性的區(qū)別

緩存一致性驗證 – AMBA CHI中的新功能

緩存一致性驗證 – AMBA CHI中的新功能

評論