高功率 PCB 布局是藝術(shù)、科學(xué)和工程的平衡,以實(shí)現(xiàn)高性能設(shè)計(jì),同時(shí)考慮與電壓間隔相關(guān)的大量限制, 系統(tǒng)布局, 產(chǎn)品尺寸, 熱要求, 以及最重要的電氣性能.從歷史上看,一個(gè)經(jīng)驗(yàn)豐富的設(shè)計(jì)師如果很好地理解這些權(quán)衡,就可以在沒有建模工具幫助的情況下提供可接受的設(shè)計(jì)。然而,在當(dāng)今采用具有非常高dv/dt和di/dt的碳化硅(SiC)MOSFET的現(xiàn)代功率轉(zhuǎn)換器設(shè)計(jì)中,了解和量化布局中的寄生效應(yīng)至關(guān)重要。在采用并聯(lián) SiC MOSFET 的設(shè)計(jì)中尤其如此,其中 PCB 寄生電感和電容會(huì)對(duì)動(dòng)態(tài)均流產(chǎn)生重大影響。是德科技的高級(jí)設(shè)計(jì)系統(tǒng) (ADS) 和電力電子專業(yè)版 (PEPro) 等電路仿真工具能夠從 PCB 布局中提取寄生元件并對(duì)其進(jìn)行建模,從而可以在構(gòu)建任何硬件之前進(jìn)行設(shè)計(jì)優(yōu)化,從而節(jié)省時(shí)間和金錢。Wolfspeed 與是德科技合作,分析了采用兩個(gè)并聯(lián)表面貼裝 SiC MOSFET 的新型 Wolfspeed 評(píng)估板的行為,并比較了仿真和測(cè)量數(shù)據(jù)。

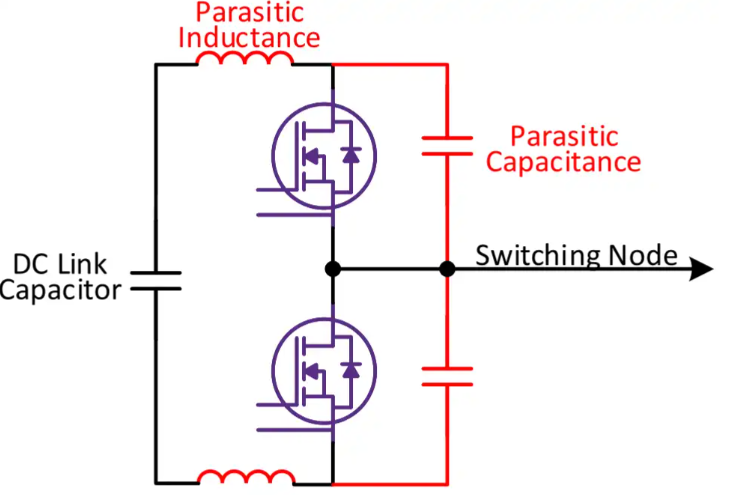

與硅 MOSFET 或 IGBT 相比,SiC MOSFET 的眾多優(yōu)勢(shì)之一是,由于快速導(dǎo)通和關(guān)斷開關(guān)邊沿,大大降低了開關(guān)損耗。更快的開關(guān)時(shí)間可實(shí)現(xiàn)更高的系統(tǒng)效率和更高的功率密度,但在PCB布局中確實(shí)需要仔細(xì)注意,以最大限度地提高優(yōu)勢(shì)。在考慮寄生元件對(duì)系統(tǒng)性能的影響時(shí),電源路徑中有兩個(gè)基本關(guān)注點(diǎn)。第一個(gè)是開關(guān)環(huán)路中的寄生電感,第二個(gè)是開關(guān)節(jié)點(diǎn)上的寄生電容。這些寄生元件在下面的圖1中以紅色顯示。

圖 1:帶有紅色寄生元件的簡(jiǎn)化半橋電路

寄生電感可能會(huì)導(dǎo)致幾個(gè)問題,具體取決于應(yīng)用。開關(guān)器件和直流母線之間的寄生電感會(huì)增加器件在關(guān)斷時(shí)的電壓過沖。PCB布局完成后,減少這種過沖的唯一方法是增加?xùn)艠O電阻,以減慢SiC MOSFET的di/dt。這將導(dǎo)致開關(guān)損耗增加。更好的解決方案是了解并優(yōu)化PCB布局,將寄生電感降至可接受的水平,以便以最佳方式驅(qū)動(dòng)MOSFET。

開關(guān)節(jié)點(diǎn)與電路中其他點(diǎn)之間的寄生電容有可能增加開關(guān)損耗、損壞信號(hào)并增加EMI。開關(guān)節(jié)點(diǎn)和母線軌之間的電容會(huì)增加開關(guān)損耗,因?yàn)榇鎯?chǔ)在寄生電容中的能量在開關(guān)事件期間消耗在MOSFET中。

在布線復(fù)雜的多層板上,很難直觀地可視化所有寄生元件及其對(duì)電路操作的影響。如果在構(gòu)建原型組件之前沒有很好地理解寄生元件,則性能可能會(huì)受到影響。潛在布局問題的警告信號(hào)是:

關(guān)斷時(shí)高壓過沖

VDS 或V GS 振鈴過多

開關(guān)損耗高于預(yù)期

并聯(lián)器件中的動(dòng)態(tài)均流失配

其中一些問題可能嚴(yán)重到足以導(dǎo)致立即設(shè)備故障或縮短系統(tǒng)的使用壽命。在原型階段發(fā)現(xiàn)這些問題意味著您已經(jīng)投入了大量的時(shí)間和金錢來訂購、構(gòu)建、測(cè)試和排除設(shè)計(jì)故障,而這些更改可能有效,也可能無效。雖然SPICE仿真器是設(shè)計(jì)和測(cè)試電路行為的有效工具,但它不考慮布局中的寄生效應(yīng)。這就是,可以使用是德科技的 PEPro 等協(xié)同仿真工具對(duì) PCB 進(jìn)行布局后分析,并在訂購任何硬件之前進(jìn)行設(shè)計(jì)更改。PEPro 使用電磁 (EM) 場(chǎng)求解器來提取 PCB 布局寄生效應(yīng)。上述潛在影響可以在這種類型的工具中看到,與花費(fèi)數(shù)月時(shí)間構(gòu)建和測(cè)試硬件原型相比,布局在數(shù)小時(shí)或數(shù)天內(nèi)得到改善。

案例研究 – 并聯(lián) MOSFET

作為 Wolfspeed 新評(píng)估板 KIT-CRD-HB12N-J1 開發(fā)過程的一部分,Wolfspeed 和是德科技合作,使用是德科技 ADS 和 PEPro 對(duì)設(shè)計(jì)進(jìn)行了分析,并將結(jié)果與實(shí)驗(yàn)室中的測(cè)量數(shù)據(jù)進(jìn)行了比較。這項(xiàng)工作展示了如何使用是德科技 ADS 和 PEPro 仿真工具預(yù)測(cè)設(shè)計(jì)的實(shí)際行為,并利用這些信息來改進(jìn)布局。

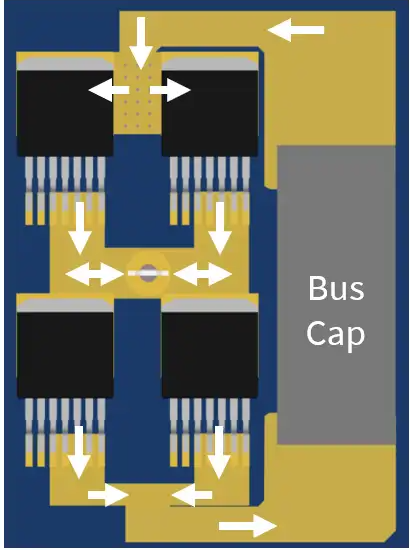

并聯(lián)分立式 SiC MOSFET 可將設(shè)計(jì)的功率水平提高到 20-60kW 水平。為了充分利用并聯(lián)MOSFET,這些器件需要幾乎同時(shí)開關(guān),并在導(dǎo)通時(shí)間內(nèi)承載幾乎相同的電流,以便它們具有相同的功率損耗。在理想系統(tǒng)中,兩個(gè)MOSFET將使轉(zhuǎn)換器可以處理的功率增加一倍。兩個(gè)器件之間的任何損耗不匹配都需要將系統(tǒng)功率從理想值降低,以保持相同的峰值結(jié)溫(TJ)。圖2顯示了兩個(gè)并聯(lián)器件的對(duì)稱電源路徑布局,這些器件配置為半橋拓?fù)洌膭?lì)并聯(lián)器件之間的均流。

圖 2:并聯(lián)半橋平衡布局示例可實(shí)現(xiàn)良好的均流

影響并聯(lián)器件之間的損耗和溫度平衡的因素有很多。第一個(gè)是MOSFET本身的參數(shù)(RDS(ON)VGS(TH)等),來自制造過程中的自然分布,設(shè)計(jì)人員無法控制。數(shù)據(jù)手冊(cè)中提供了這些參數(shù)的范圍,需要對(duì)設(shè)計(jì)進(jìn)行一些降額,以解決并聯(lián)器件之間潛在的不匹配問題。但是,設(shè)計(jì)人員可以控制的兩個(gè)因素,即布局和冷卻系統(tǒng),可能會(huì)對(duì)并行器件之間的性能和平衡產(chǎn)生更大的影響。

許多碳化硅 MOSFET 參數(shù)與溫度有關(guān)。即使并聯(lián)設(shè)備的電氣布局完美平衡,冷卻系統(tǒng)也會(huì)引入不平衡。如果冷卻系統(tǒng)由于熱堆疊、流動(dòng)不平衡或靠近其他熱源而無法為所有設(shè)備提供相同的冷卻,則設(shè)備將在不同的溫度下運(yùn)行。為了滿足可靠性要求,設(shè)計(jì)人員必須限制轉(zhuǎn)換器的操作,以將最熱器件保持在應(yīng)用所需的TJ以內(nèi),從而導(dǎo)致其他器件的利用率不足。

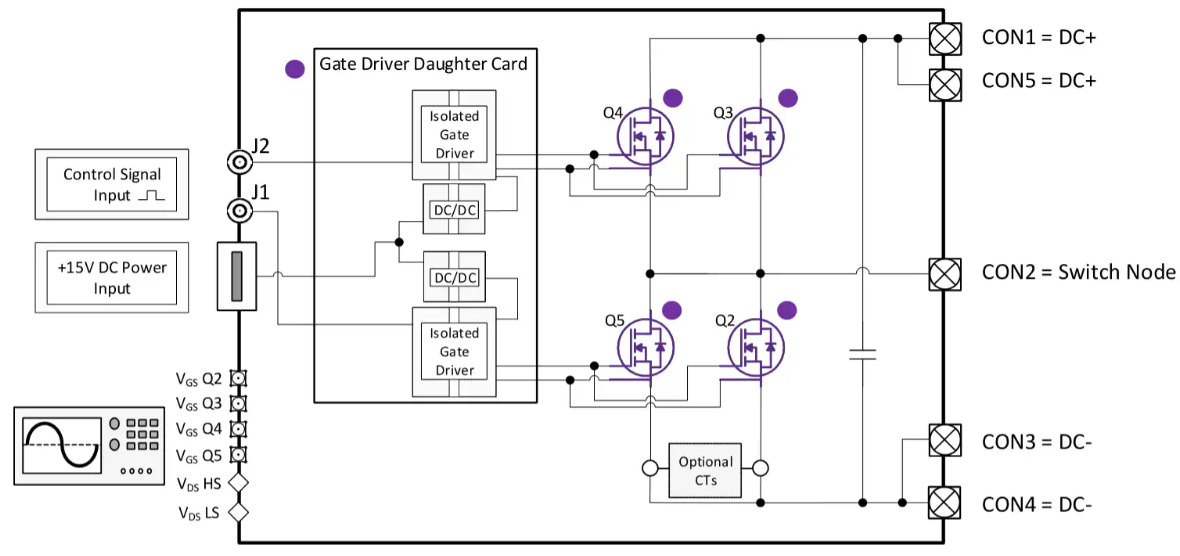

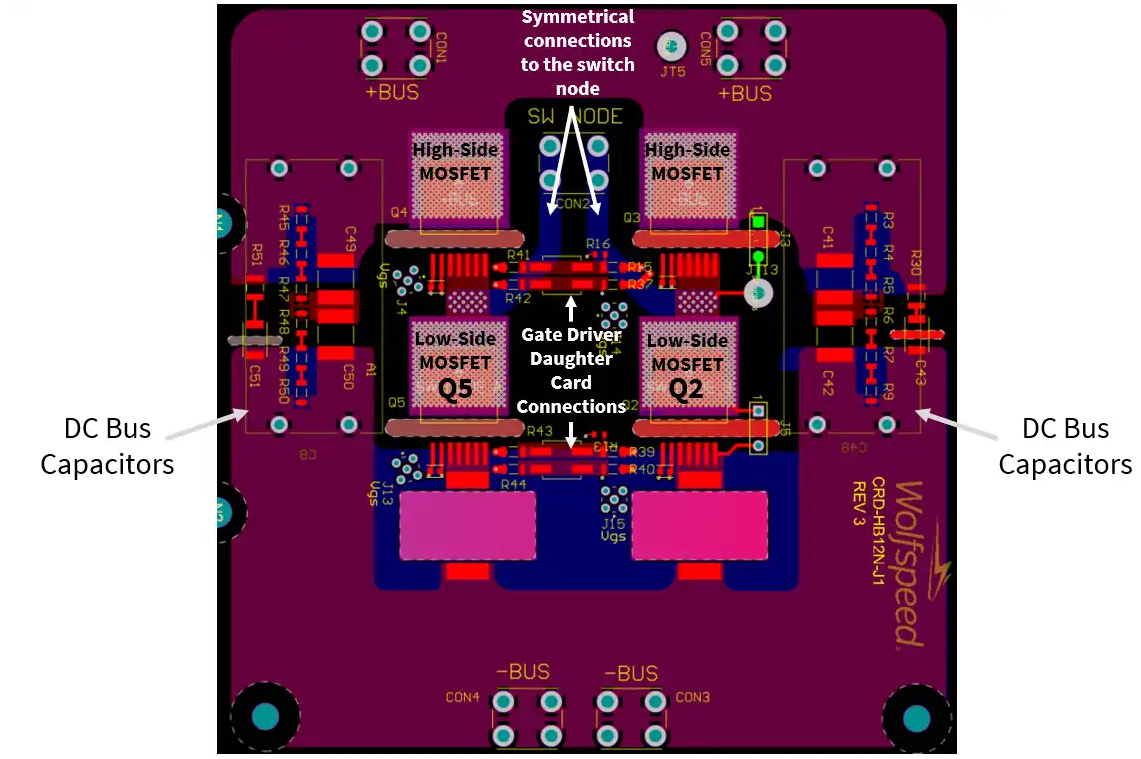

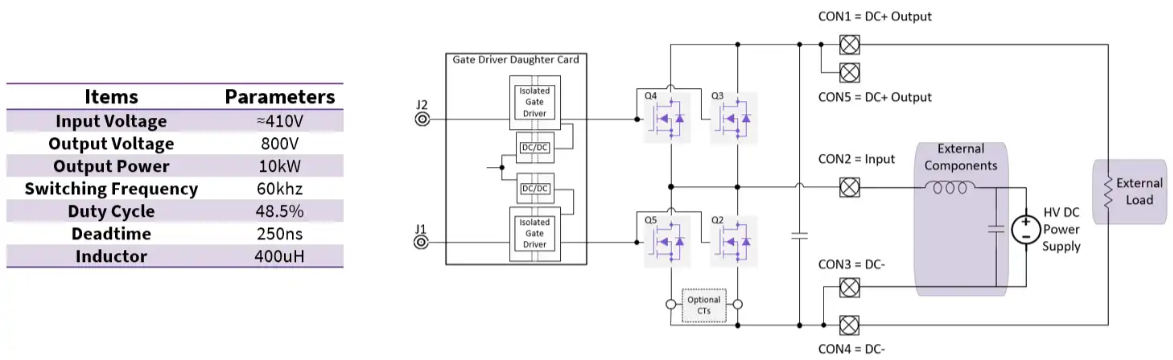

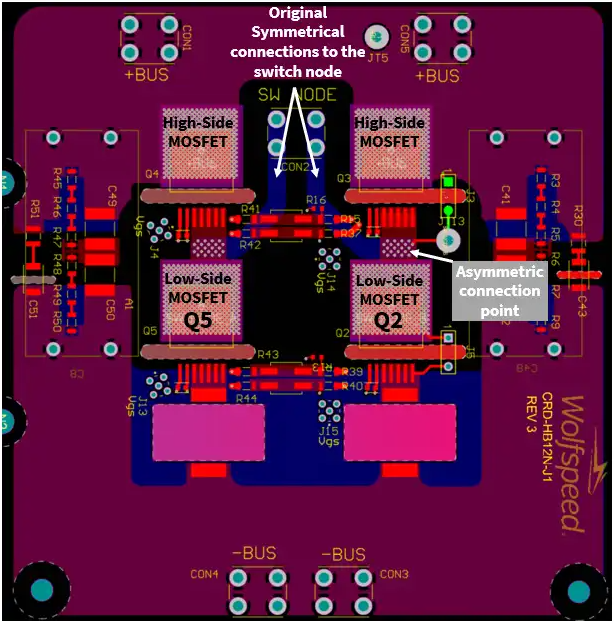

PCB布局是設(shè)計(jì)人員對(duì)設(shè)計(jì)擁有最多控制權(quán)的領(lǐng)域,因此對(duì)性能的影響是好是壞的能力也最大。正是在這里,是德科技的 PEPro 仿真工具可以有效地測(cè)試潛在布局、識(shí)別問題和快速開發(fā)解決方案。Wolfspeed 的 KIT-CRD-HB12N-J1 是一款半橋評(píng)估板,每個(gè)開關(guān)位置有兩個(gè)并聯(lián)的 MOSFET。該板使用子卡柵極驅(qū)動(dòng)器。下圖顯示了電路板的框圖原理圖和電源部分布局的概述。

圖 3a:KIT-CRD-HB12N-J1 評(píng)估板框圖

圖 3b:KIT-CRD-HB12N-J1 功率部分布局,顯示 Q5 和 Q2 的對(duì)稱性和位置

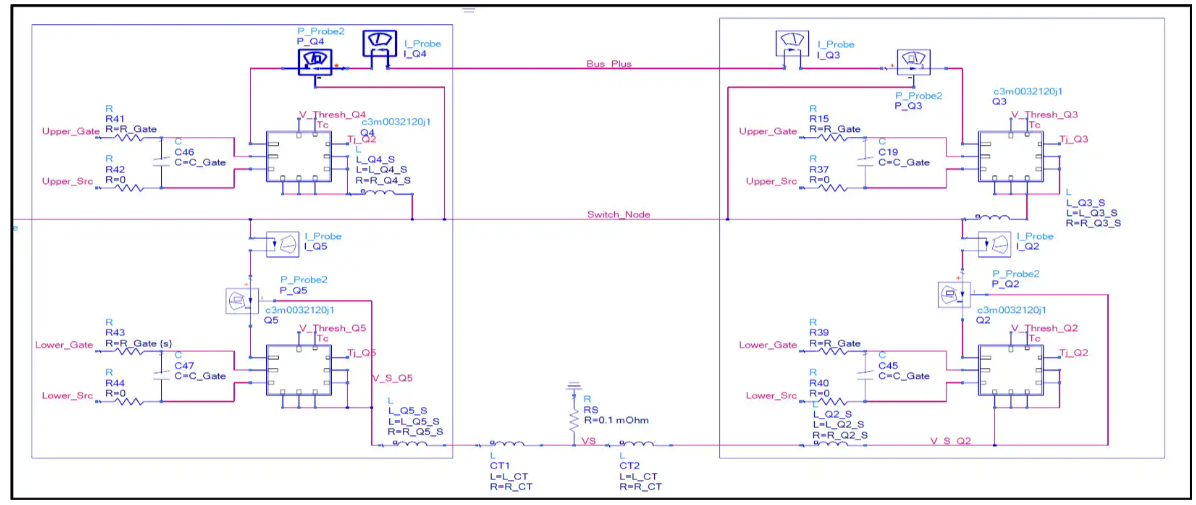

是德科技在該評(píng)估板上為電路的電源部分開發(fā)了一個(gè) ADS 工作區(qū)。本練習(xí)未對(duì)低壓和柵極驅(qū)動(dòng)電路進(jìn)行建模,因?yàn)橹攸c(diǎn)是電源路徑的對(duì)稱性。

圖 4:是德科技 ADS 工作區(qū),顯示 KIT-CRD-HB12N-J1 電源電路

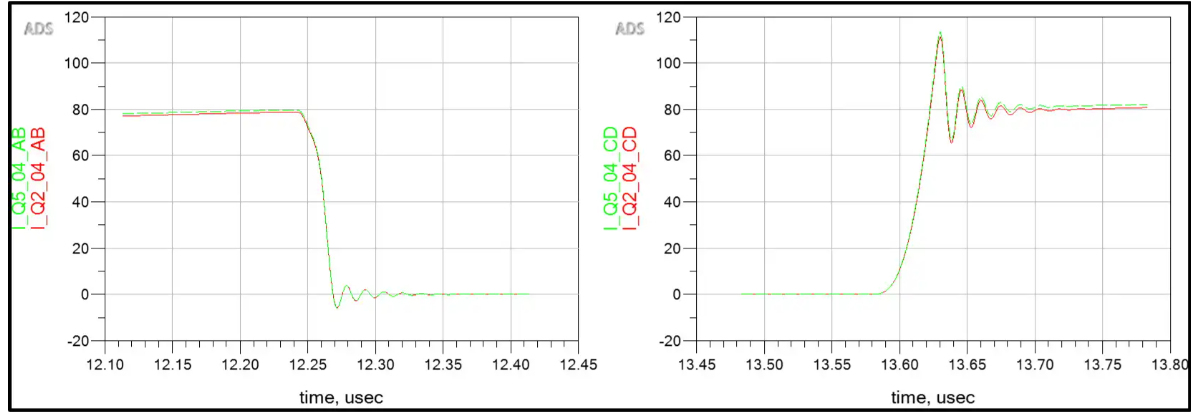

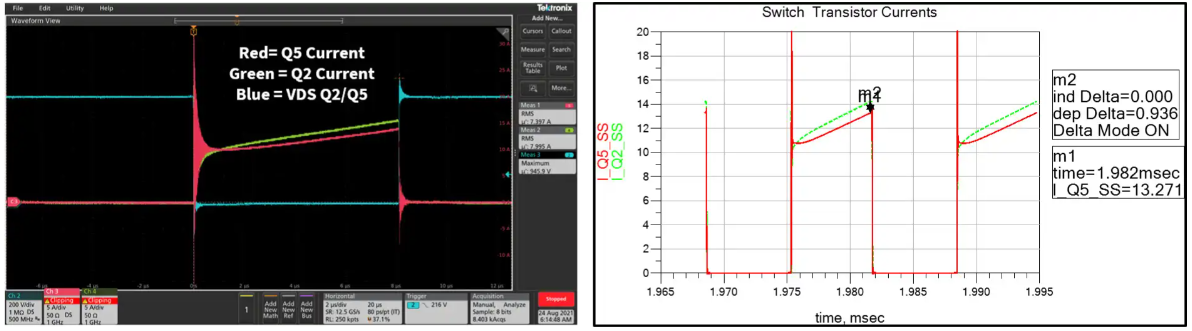

該評(píng)估板可用于在 SiC MOSFET 上執(zhí)行開關(guān)損耗測(cè)量。每個(gè)并聯(lián)MOSFET都有一個(gè)單獨(dú)的電流傳感器,因此可以分析每個(gè)器件的動(dòng)態(tài)電流以檢查均流。如果布局不對(duì)稱,導(dǎo)致每個(gè)并聯(lián)器件的寄生電感或電容不同,則兩個(gè)器件之間導(dǎo)通和關(guān)斷時(shí)的電流將不匹配。下面顯示的是德科技仿真顯示了兩個(gè)并聯(lián)的下部碳化硅MOSFET中的電流。從該仿真中可以清楚地看出,開關(guān)邊沿兩個(gè)器件之間的電流不匹配非常小。這表明兩個(gè)設(shè)備的布局非常對(duì)稱。

圖 5:關(guān)斷(左)和導(dǎo)通(右)時(shí) Q2 和 Q5 中的仿真電流

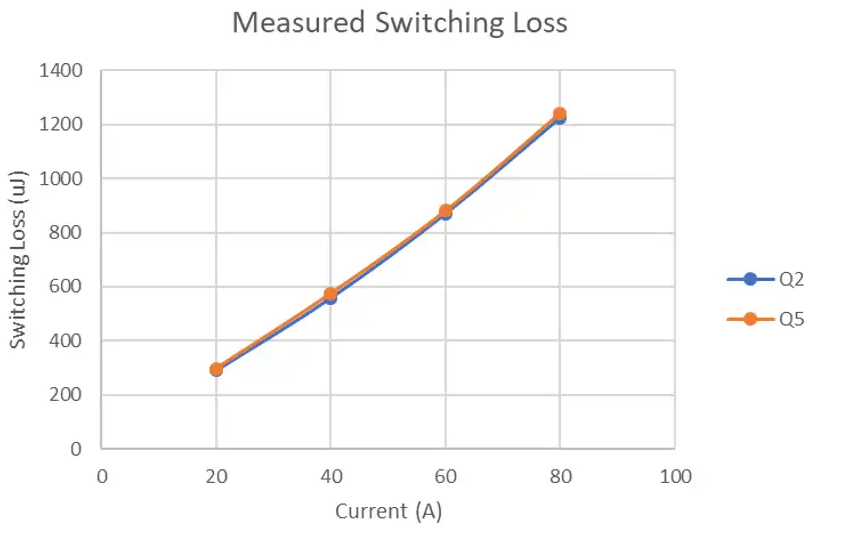

實(shí)驗(yàn)室的測(cè)量結(jié)果證實(shí)了模擬是正確的。這兩個(gè)器件的開關(guān)損耗幾乎相同,如下圖所示。

圖 6:在不同電流下測(cè)得的 Q2 和 Q5 開關(guān)損耗

接下來,在作為同步升壓轉(zhuǎn)換器運(yùn)行的背景下分析該板,如下所示。

圖 7:KIT-CRD-HB12N-J1 的同步降壓轉(zhuǎn)換器配置

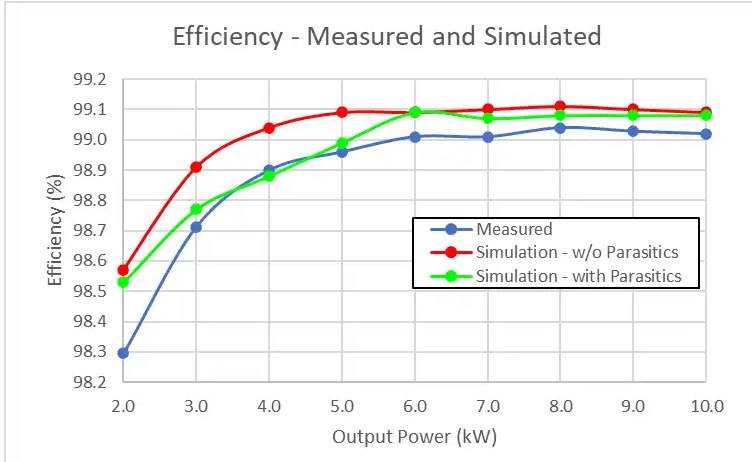

在對(duì)PCB的寄生元件進(jìn)行建模和不對(duì)PCB寄生元件進(jìn)行建模的情況下,對(duì)效率進(jìn)行了仿真。不包含寄生元素的分析是SPICE模型本身所能做到的。如圖所示,包括寄生元件會(huì)降低效率,并且模型更接近實(shí)驗(yàn)室中看到的測(cè)量結(jié)果。對(duì)于試圖滿足非常嚴(yán)格的效率要求的設(shè)計(jì)人員來說,這是一個(gè)重要的考慮因素。布局會(huì)對(duì)損失產(chǎn)生重大影響。

圖 8:同步升壓配置中的實(shí)測(cè)效率與仿真效率

最后,進(jìn)行了一次實(shí)驗(yàn),有意在設(shè)計(jì)中引入不對(duì)稱性,以查看對(duì)硬件和仿真的影響。在原始布局中,與升壓電感的開關(guān)節(jié)點(diǎn)連接在兩個(gè)并聯(lián)支路之間對(duì)稱。對(duì)于此測(cè)試,連接點(diǎn)移至Q2的漏極卡舌處,從而將電阻和電感降低到Q2,并將其增加到Q5。

圖 9:有意引入的非對(duì)稱交換節(jié)點(diǎn)連接

這種不對(duì)稱導(dǎo)致第二季度的損失增加。對(duì)Q2電阻的增加會(huì)導(dǎo)致更多的電流在導(dǎo)通時(shí)間內(nèi)流過Q5,從而導(dǎo)致更高的傳導(dǎo)損耗。在測(cè)試的場(chǎng)景中,Q2故意具有比Q5更低的VGS(TH),因此盡管布局不對(duì)稱,但Q2仍然更早開啟并占用更多的動(dòng)態(tài)電流。是德科技 ADS 能夠捕獲這兩種現(xiàn)象,并且與測(cè)量的實(shí)驗(yàn)室數(shù)據(jù)非常吻合。

圖 10:采用非對(duì)稱連接的 Q2 和 Q5 中測(cè)量(左)和仿真(右)電流波形

像這樣的不對(duì)稱性通常被放置在設(shè)計(jì)中,以滿足其他設(shè)計(jì)目標(biāo),例如連接點(diǎn)的位置。然而,正如是德科技 ADS 所證明的那樣,這可能會(huì)對(duì)設(shè)計(jì)性能產(chǎn)生重大影響。使用這樣的工具可以幫助設(shè)計(jì)人員了解設(shè)計(jì)中的所有權(quán)衡,并避免在測(cè)試階段出現(xiàn)意外。

結(jié)論

碳化硅MOSFET和二極管為更高效、功率密度更高的設(shè)計(jì)打開了大門,這在很大程度上是因?yàn)樗鼈兊目焖匍_關(guān)能力。然而,隨著開關(guān)速度的提高,設(shè)計(jì)人員越來越需要了解布局中的寄生元件,這些元件會(huì)對(duì)性能產(chǎn)生重大影響。將電磁建模與 SPICE 建模相結(jié)合,可以更全面地了解功率轉(zhuǎn)換器的行為。這些工具可以避免較長(zhǎng)的原型設(shè)計(jì)周期,并優(yōu)化系統(tǒng)的整體性能,從而縮短設(shè)計(jì)時(shí)間。

審核編輯:郭婷

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

9419瀏覽量

156402 -

SiC

+關(guān)注

關(guān)注

32文章

3726瀏覽量

69440 -

PCB

+關(guān)注

關(guān)注

1文章

2309瀏覽量

13204

發(fā)布評(píng)論請(qǐng)先 登錄

使用寄生建模軟件了解和優(yōu)化碳化硅功率PCB布局

使用寄生建模軟件了解和優(yōu)化碳化硅功率PCB布局

評(píng)論