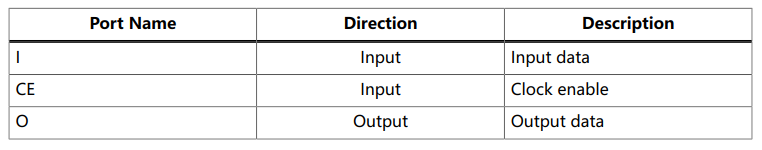

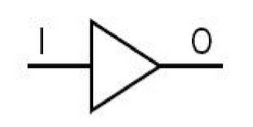

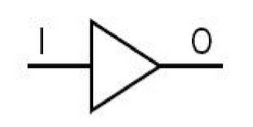

易靈思提供了原語文檔,可以查看每個原語。經常有人會問,如果普通的GPIO怎么走全局時鐘網絡,其實很簡單,打開原主文檔,找到EFX_GBUFCE,該部分提供了verilog和VHDL的用法。

EFX_GBUFCE既可以讓GPIO走全局時鐘網絡也可以用于為時鐘添加使能控制,當并不是隨時需要該時鐘時可以把時鐘禁止以節省功耗。

CE_POLARITY用于指示CE是高有效還是低有效,如果為1則高有效,反之則低有效。

CE是時鐘O的輸出使能。

EFX_GBUFCE # ( .CE_POLARITY(1'b1) // 0 active low, 1 active high ) EFX_GBUFCE_inst ( .O(O), // Clock output to global clock network .I(I), // Clock input .CE(CE) // Clock gate );

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

GPIO

+關注

關注

16文章

1328瀏覽量

56228 -

時鐘網絡

+關注

關注

0文章

16瀏覽量

6700 -

VHDL電路

+關注

關注

0文章

4瀏覽量

1497

原文標題:GBUFCE原語

文章出處:【微信號:gh_ea2445df5d2a,微信公眾號:FPGA及視頻處理】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

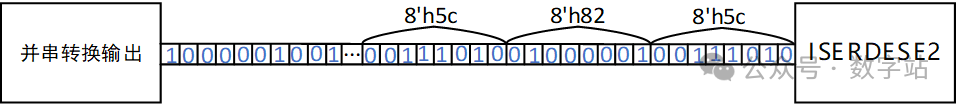

ISERDESE2原語端口及參數介紹

前面在講解HDMI接口之前,講解過IDDR、ODDR、OSERDESE2、IBUF等原語,之后一直有讀者在問什么時候更新ISERDESE2這個原語。前文講解過這些原語都在HDMI或者RGMII中使用過,但是ISERDESE2這個

Xilinx中的原語作用是啥啊?

我看到別人寫的項目 程序中用了很多原語,比如輸入時鐘要設置一個IBUFG,有一些輸出信號接一個OBUFG,那么原語的好處是什么?如何知道什么時候要使用原語!

發表于 07-13 19:59

如何從Virtex原語切換到Spartan原語?

親愛的大家,Virtex中的許多原語在Spartan 6中找不到,例如BUFIO,BUFR,IDELAY,IDDR。如何使用Spartan原語實現類似的功能?非常感謝你!箱子以上來自于谷歌翻譯以下

發表于 06-03 10:31

Xilinx FPGA常用原語介紹

項目中主要用到的原語與IO端口有關,所以基本在Input/Output Functions 和IO兩類中。下面著重介紹實際中所用到的幾個原語,芯片A7系列。

發表于 01-06 11:23

?1.7w次閱讀

基于URAM原語創建容量更大的RAM

UltraRAM 原語(也稱為 URAM)可在 Xilinx UltraScale +? 架構中使用,而且可用來高效地實現大容量深存儲器。

發表于 07-13 11:08

?8646次閱讀

Xilinx原語使用方法有哪些

Xilinx公司的原語按照功能分為10類,包括:計算組件、I/O端口組件、寄存器和鎖存器、時鐘組件、處理器組件、移位寄存器、配置和檢測組件、RAM/ROM組件、Slice/CLB組件以及G比特收發器組件。下面分別對其進行詳細介紹。

Xilinx原語使用方法

Xilinx公司的原語按照功能分為10類,包括:計算組件、I/O端口組件、寄存器和鎖存器、時鐘組件、處理器組件、移位寄存器、配置和檢測組件、RAM/ROM組件、Slice/CLB組件以及G比特收發器組件。下面分別對其進行詳細介紹。

發表于 03-24 06:14

?4次下載

Verilog HDL指定用戶定義原語UDP的能力

在前一章中,我們介紹了Verilog HDL提供的內置基本門。本章講述Verilog HDL指定用戶定義原語U D P的能力。

GBUFCE原語介紹

GBUFCE原語介紹

評論