當今時代,隨著云計算、AI、高性能計算等技術的發展,海量的數據從互聯網的不同節點被匯集、處理、再分發,對存儲、DPU、GPU、服務器等芯片在數據容量、速率、部署靈活性等方面提出了新的要求。結合Cloud AI、云計算向邊緣網絡的擴展趨勢,又延伸出更加豐富的應用場景,使得數據可以更快更好地為人們提供服務和各種決策的輔助。

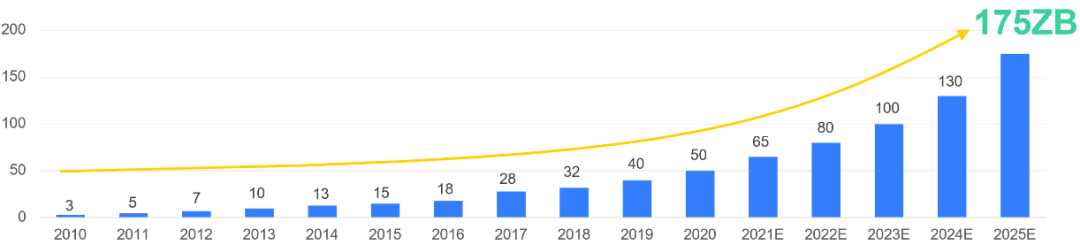

這些創新領域都需要處理大量的數據及計算。據IDC統計,2025年全球數據量將達到175ZB,對算力的要求每年增加10倍。換句話說,高算力的發展,成為支撐數字化世界的重要推手之一,是推動未來經濟發展的重要指標與技術。

全球數據量年度規模及預測

(單位:ZB;來源: IDC)

高速增長的數據量,推動了更多加速器和計算架構的布局。在此背景下,通過數據接口技術的不斷演進來滿足上述應用對新性能和容量的需求,正在成為核心的關鍵技術。

因此,高速接口技術開始得到廣泛使用,比如DDR、LPDDR、PCIe、CXL等,接口上的性能在不斷地提升,標準的演進和更新周期也在不斷地縮短。

“

數據安全是重中之重

與之伴隨而來的,是數據安全保護的重要性被提到了一個新的高度。因為隨著新應用的出現,很多數據包含隱私、敏感信息,同時由于不同人的數據可能會存儲在同一個資源池當中,這就給數據竊取、篡改,甚至是偽造帶來了比較高的風險。

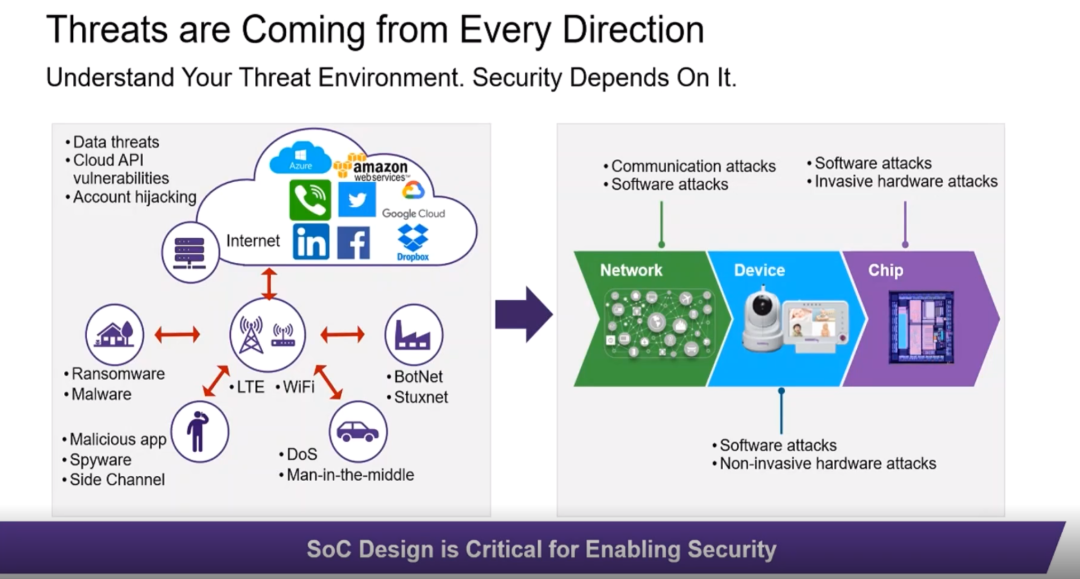

數據安全威脅來自四面八方。尤其隨著當前密碼分析技術、儀器自動化和量子計算等技術的發展,相比過去的攻擊手段,攻擊門檻已大大降低。

對此,通過政策法規和安全技術標準的演進,能夠對數據安全問題加以限制和約束。以技術標準為例來看,PCIe和CXL組織在2020年底發布的最新標準當中首次加入了信息安全的功能——PCIe 5.0和CXL 2.0當中的IDE(Integrity and Data Encryption)數據完整性和加密保護。此外,下一代的PCIe 6.0、CXL 3.0當中的安全需求也得到進一步的強化。

這些都證明了數據安全接口的需求和重要性。除了最直觀的性能、功耗、成本等指標外,數據安全作為一個重要的評判標準已經愈發成為了行業的技術共識。

“

高速接口成為實現數據安全的關鍵

從芯片開發者的角度來說,為了有效地保護芯片內的核心資產和數據安全,SoC設計是實現安全的關鍵。面對上述可能出現的數據安全威脅,芯片開發者需要關注攻擊技術的演進,盡早在芯片設計中提前做出應對。

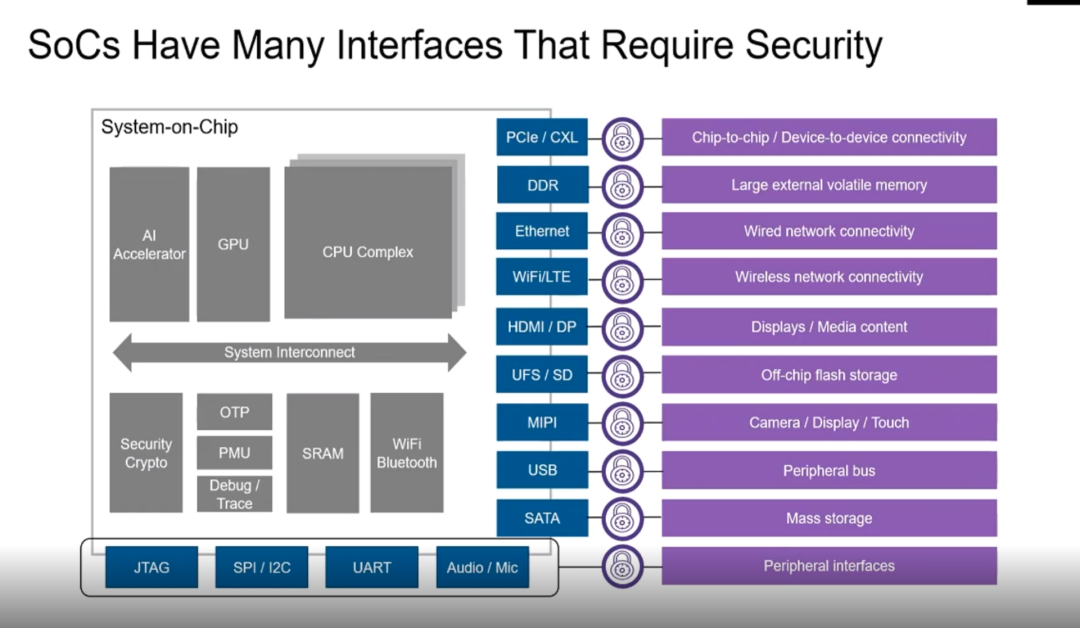

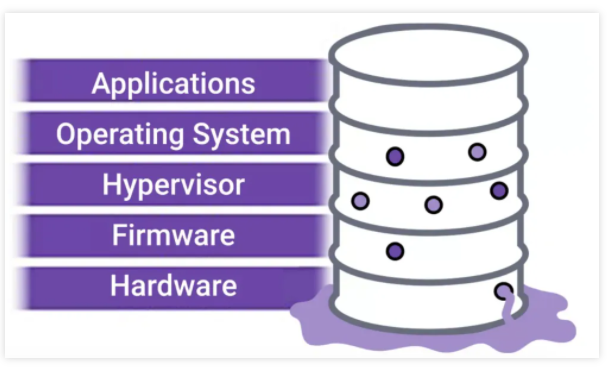

具體到芯片架構層面,各種接口作為芯片和外部世界的交互媒介,長期以來都是攻擊者所關注的重要對象。行業最新的發展方向就是將安全功能融入到數據接口來實現傳輸和保護的高效結合。

如下圖所示,芯片上有許多需要安全性的接口。

PCIe/CXL接口廣泛用于實現芯片系統之間的高速互聯,更是為Chiplet互連(UCIe)提供了堅實的技術基礎;

DDR作為常用的存儲媒介接口,安全需求非常清晰,一個典型的應用場景就是,當敏感信息寫入DDR時會被加密存儲,在讀取載入芯片的時候才被解密恢復;

Ethernet、WiFi、LTE等有線、無線的網絡接口,其技術標準本身已經是在不同的傳輸層去定義了安全協議來確保數據包的機密性、完整性和真實性;

HDMI/DP作為廣泛使用的多媒體接口,它的安全需求主要來自于影音內容的版權保護,通過利用行業中比較成熟的HDCP 標準就可以很有效地保障版權影音在合法合規的設備中完成端到端傳輸,這也是全球影視創作傳播得以持續健康發展的核心技術保障;

一些其他的接口,比如MIPI、USB等,基本上也已經有了標準化的數據安全保護技術,或是正在一些內部小組的主導之下,參考其他接口的案例來積極地草擬相關的安全協議。

整體而言,未來芯片數據接口的發展方向就是形成一個標準化、專門化的安全防護,來保證不同廠商的設備通過同類型接口在互通的基礎之上強化各個數據鏈路上的信息安全。

那么怎樣才能算是一個有效、完整的安全保護方案呢?

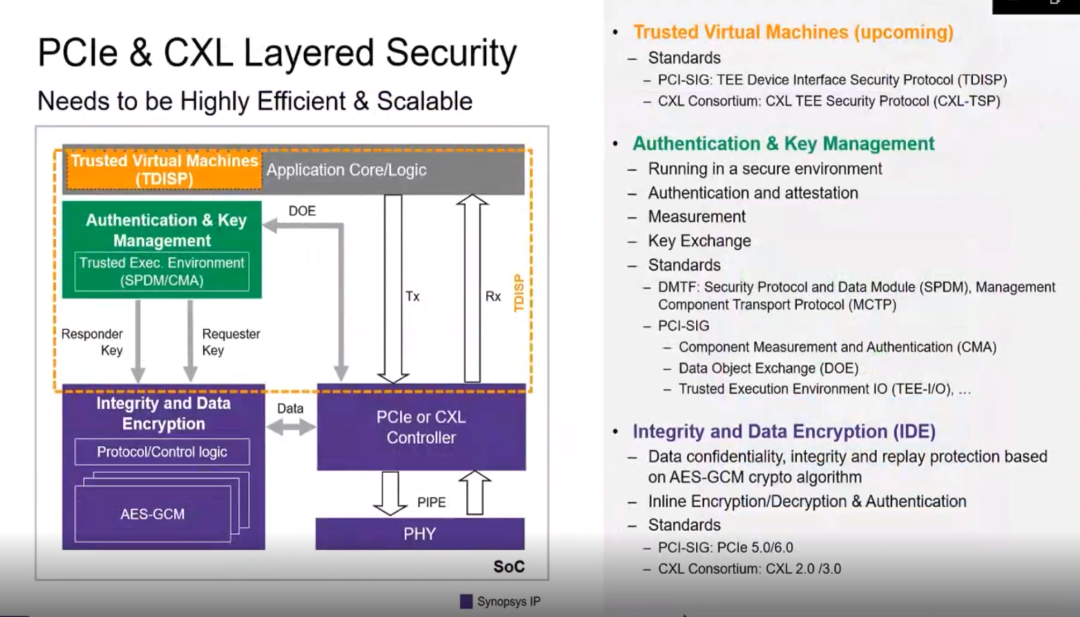

從本質上來說,一個優秀的安全保護方案需要具備兩個核心要素:第一是認證鑒權以及密鑰管理;第二是從端到端的數據完整性和機密性的保護。

認證鑒權以及密鑰管理:認證鑒權和密鑰管理模塊的主要功能是在通訊節點之間實現身份認證以及安全能力的識別,確保通訊雙方是可信任的,并且能夠協商產生相應的密鑰來支持后續的加解密操作。

數據完整性和機密性保護:在認證鑒權完成、確定這個設備的合法身份之后,負責對實際傳輸的數據進行加密保護,以防止數據被竊取或篡改。

除了這兩個核心要素之外,在系統層面還有一個潛在需求,即上述功能要在一個受信任的安全邊界內部來實現,即需要一個可信執行環境。從控制層面,比如安全啟動、密鑰管理等任務也要確保上述的鑒權和傳輸操作按照設計初衷來正確、安全地執行。

另外,一個優秀的安全防護方案還需要考慮到整體的性能、功耗、面積、成本(PPA)方面的影響和優化。比如在保護數據通路的同時,如何盡可能降低對通訊延遲的影響?在建立身份信任的時候,如何盡可能減少額外的通訊開銷?在進行安全密鑰管理的時候,如何盡可能降低面積的增加?……這些都給芯片開發者提出了新的挑戰。

“

高速接口IP如何為數據安全賦能?

基于上述內容,以PCIe/CXL標準所定義的最新的安全規范為例,充分反映了安全設計理念在高速接口上的實現。

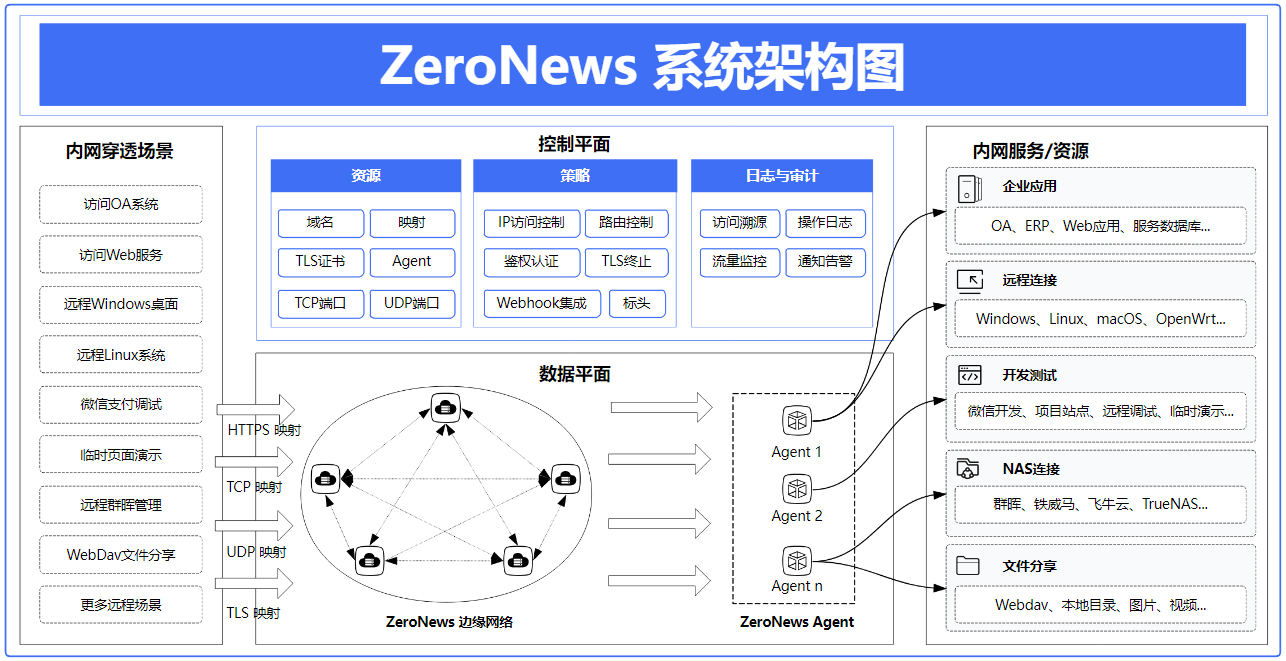

在接口IP設計中,首先需要一個運行在可信執行環境之下的設備認證和密鑰管理模塊,以及一個數據完整性和機密性的保護模塊,來對鏈路上傳輸的大量數據進行保護。目的是為了增強系統的安全魯棒性,防止數據的竊取、篡改、重放、惡意注入、刪除等。

具體來看,上面框圖從上到下分層描述了從應用層到硬件層幾個主要的組成部分,來管理虛擬機和虛擬外設之間的信任關系,以及在PCIe、CXL上實現設備的認證和密鑰協商,不僅要確認硬件設備的身份,同時還要驗證軟件、固件的真實性。

在建立設備之間的這種信任之后,在IDE標準的指導之下,在硬件層面上就要對鏈路上傳輸的數據進行在線的加解密處理。

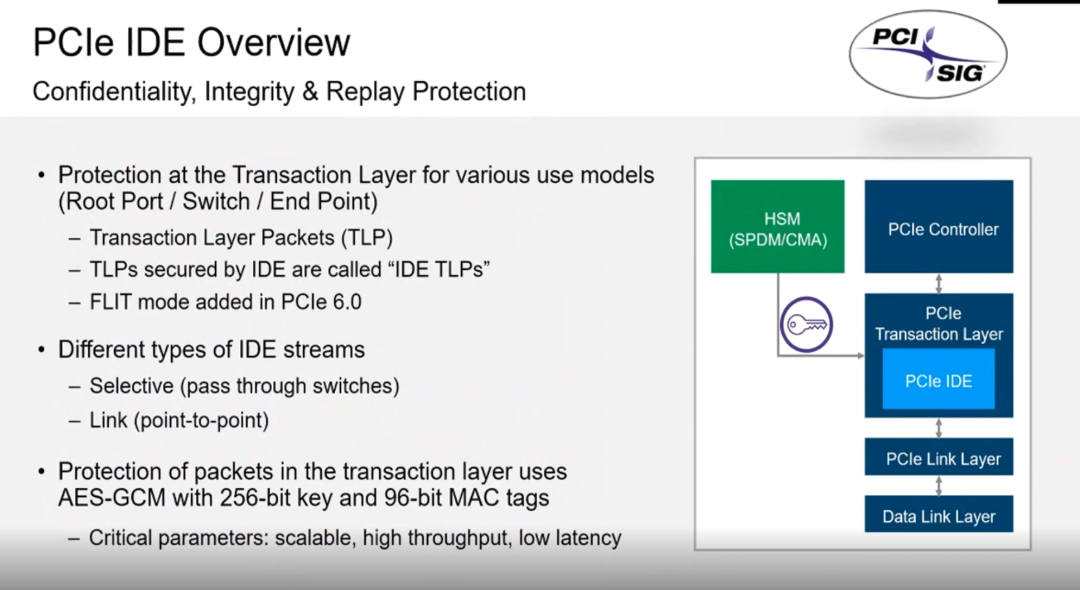

上文有提到,IDE是在2020年底PCIe 5.0發布的ECN當中所定義的,其功能是在傳輸層實現數據的完整性、機密性以及重放保護,可以支持包括Root Port/Switch/End Point等在內的不同應用場景。

IDE所處理的數據單元是PCIe傳輸的TLP包,而且在PCIe 6.0當中,將會看到以FLIT為單元的FLIT模式。

IDE所處理的數據可以分為Selective stream和Link stream兩種不同的數據流。Selective IDE stream可以有選擇性的對傳輸的TLP數據進行保護,并且可以穿越中間的Switch設備;而Link IDE stream會對所有TLP的數據進行加密保護,保護的是直連鏈路上的數據。

另外,IDE標準要求采用廣泛部署的AES-GCM算法,256 bit的密鑰長度,添加96 bit的完整性標識。IDE統一的功能定義和加密算法對于建立行業規范來確保不同廠商的設備之間互通互聯非常重要。

“

新思科技IP為芯片數據安全保駕護航

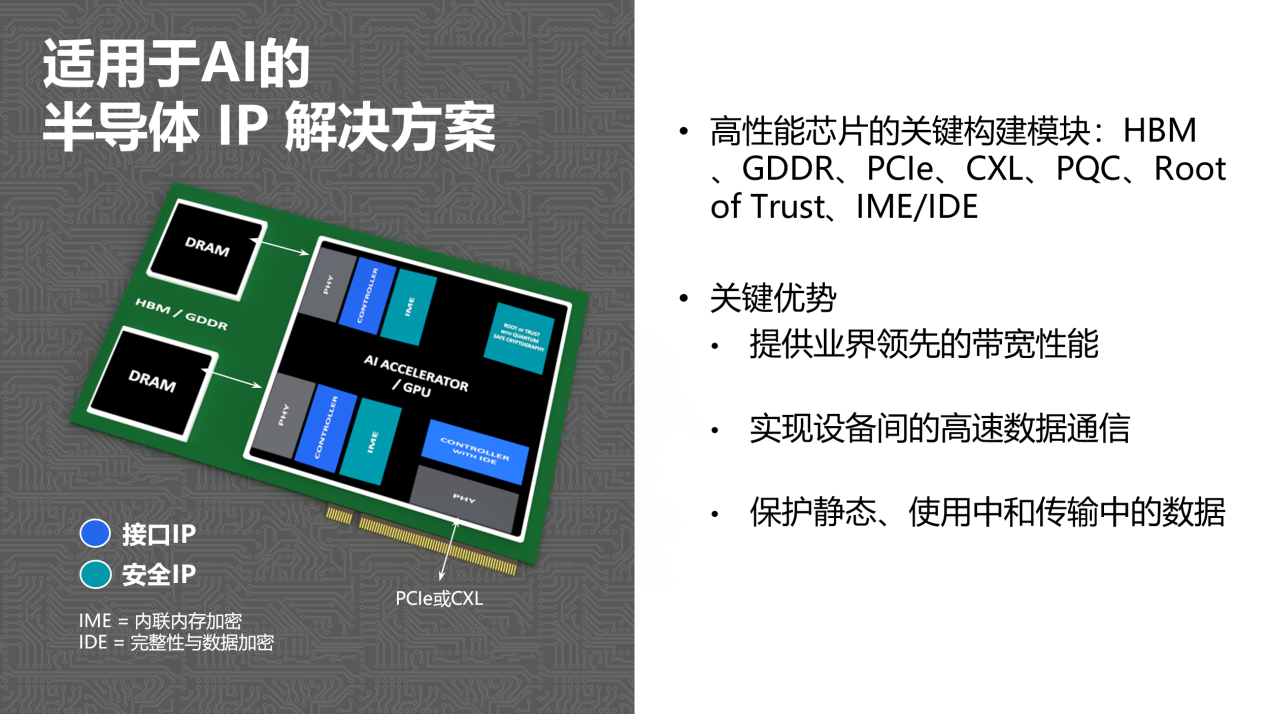

作為半導體IP行業的領先企業,新思科技全面賦能芯片設計,擁有全線高速接口IP產品以支持高性能計算需要的高帶寬、大吞吐量、低延遲及數據安全的需求。

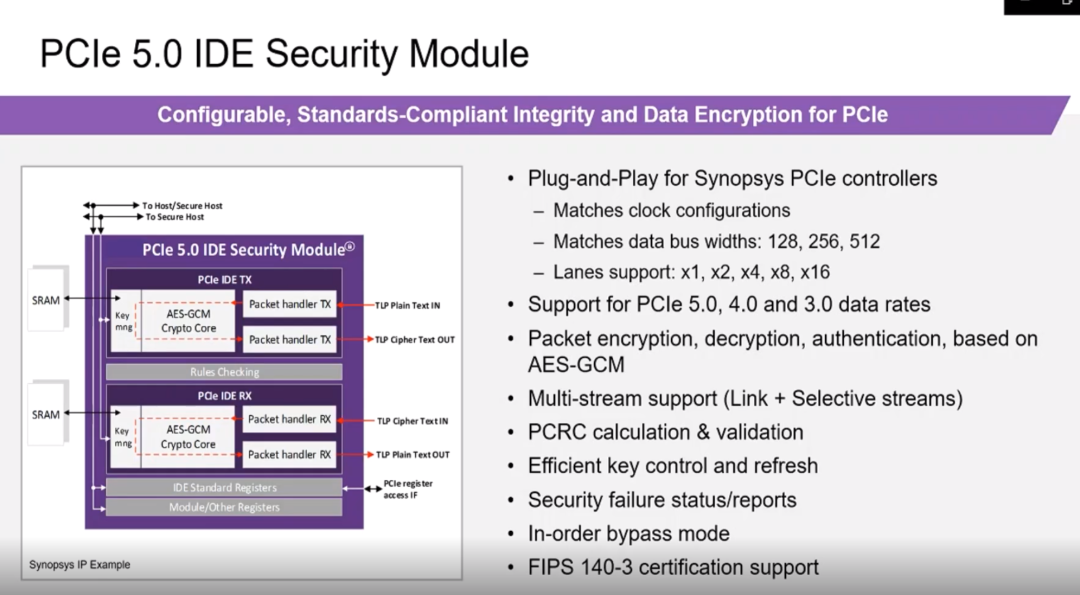

以新思科技針對PCIe設計的IDE IP產品為例,該IP支持TX和RX兩個方向的數據保護,內部的AES- GCM引擎可以通過優化來匹配PCIe controller的傳輸速率。同時,它也是高度可配置的,以滿足PCIe接口在不同芯片中的配置需求。

據新思科技技術專家介紹,IDE IP有專門的密鑰接口用于和安全環境對接,從而支持比較高效的密鑰切換,在實際使用場景中,根據數據類型的不同可以支持不同的密鑰來進行相應的保護。

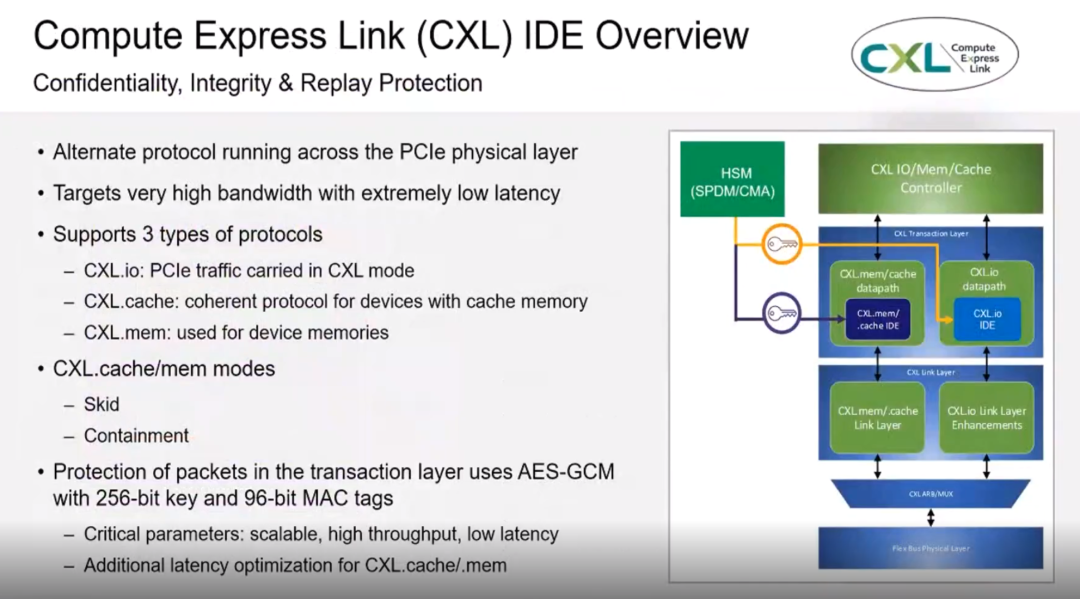

與PCIe類似,CXL協議也是于2020年年底在2.0版本當中同期發布了IDE的ECN。CXL以PCIe的物理層為基礎,可以在host和device之間提供高吞吐率、低延遲以及緩存一致性等特性。

CXL標準自推出以來,越來越多地部署在高速存儲、云計算的應用場景當中,比如數據中心的存儲資源池、智能IO擴展卡,異構計算架構下的加速器等。類似于PCIe的IDE,CXL的IDE也是使用標準的256 bit AES-GCM,添加96 bit的完整性校驗。

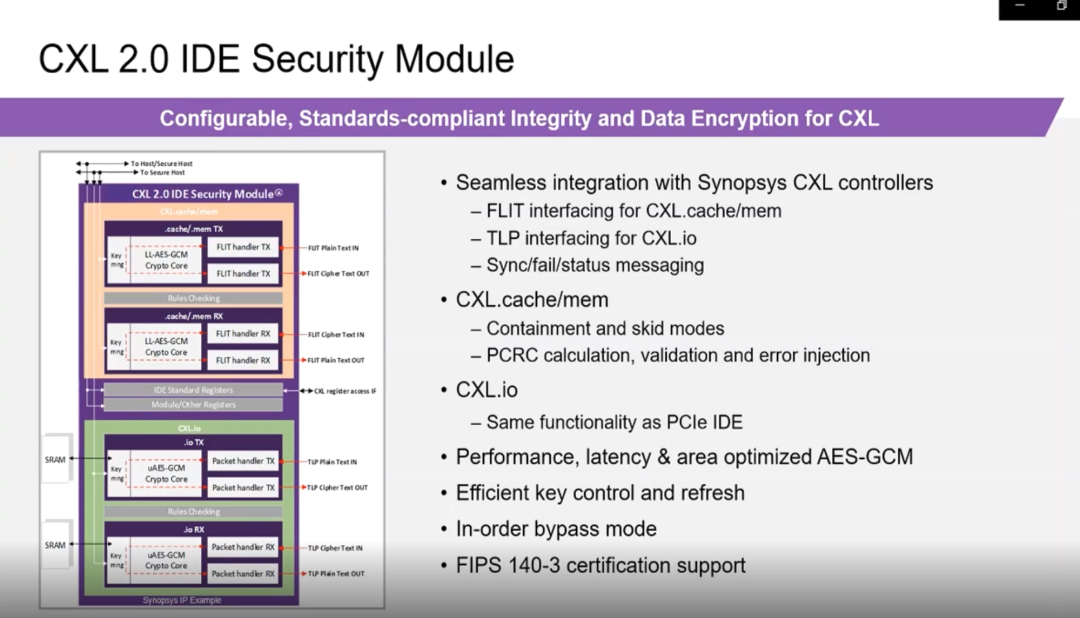

針對CXL,新思科技同樣設計了IDE的IP產品。從示意圖來看,CXL的功能模塊基本上和PCIe的IDE一致。而對于CXL cache、mem,IDE針對CXL FLIT數據包的傳輸特點加入了新的模塊來優化它的延遲。

CXL IDE同樣支持TX和RX兩個方向的數據保護,內部的AES-GCM的引擎經過優化之后可以匹配CXL controller的傳輸速出率。同時IDE IP也是高度可配置的,可以去滿足CXL在不同芯片當中的配置需求。同時,IO、mem、cache對應的IDE也可以支持其任意組合,從而滿足不同設備類型和業務場景。

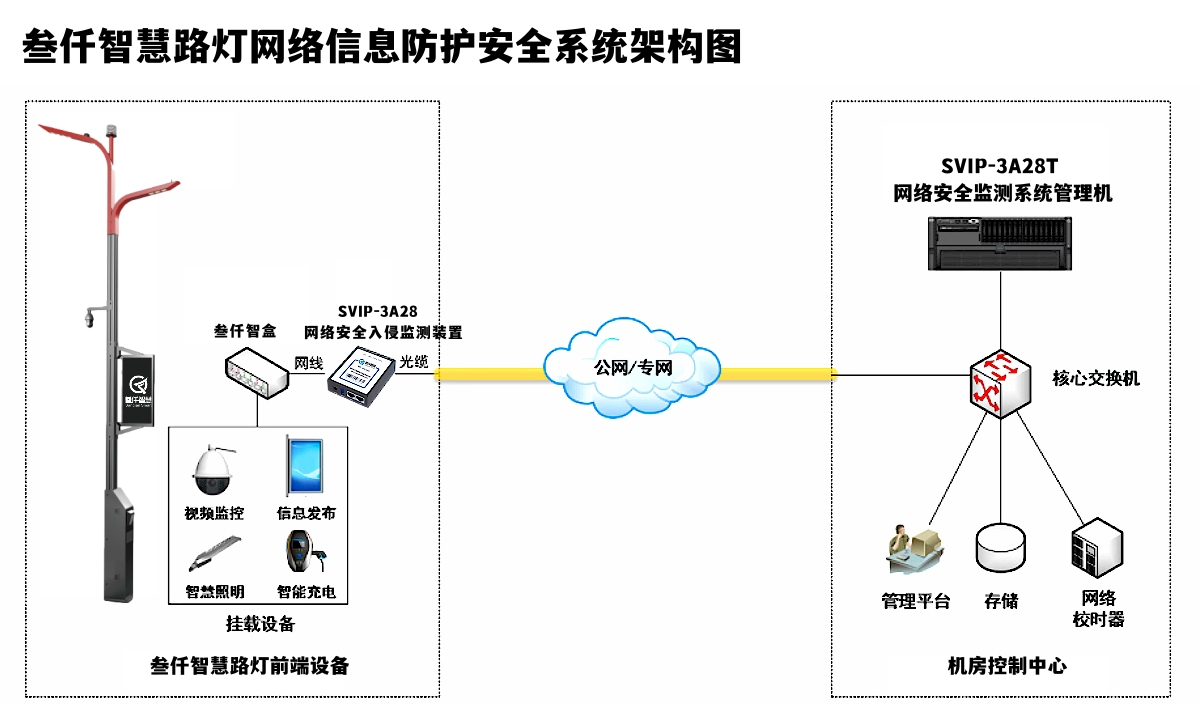

除了PCIe、CXL IDE之外,接口安全作為一個被普遍采納的設計集成趨勢,在其他的基礎協議上也有所體現。

比如針對包括DDR/LPDDR在內的各種存儲接口,在行業中定義了AES-XTS算法模式來對其中的靜態數據進行保護,為了降低相關加解密操作的延遲開銷,可以把密碼算法模塊集成到存儲控制器的數據通路內部,從而實現所謂的“內嵌”,或者說在線的數據保護,也就是IME (Inline Memory Encryption)的功能。

對于芯片開發者來說,新思科技既可以提供內置IME功能的DDR/LPDDR控制器,也可以提供單獨的IME IP來支持用戶自行集成到不同的存儲接口上面,來保證敏感信息不會以明文的方式離開芯片。

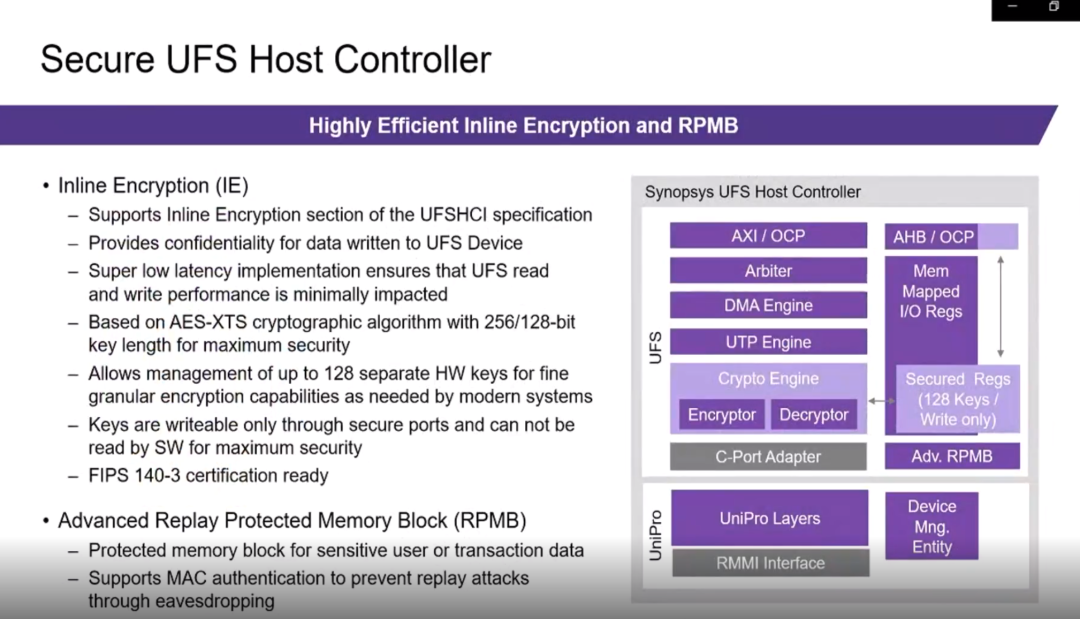

針對UFS,新思科技可以提供內嵌硬件加密功能的UFS控制器,支持標準的AES-XTS算法值和內嵌結構,來降低安全防護對原有數據傳輸的性能影響。

此外,UFS控制器還專門支持RPMB功能,可以有效地對內部存儲的核心數據進行訪問權限管理,并且利用校驗技術來防止數據被竊取之后的重放攻擊。

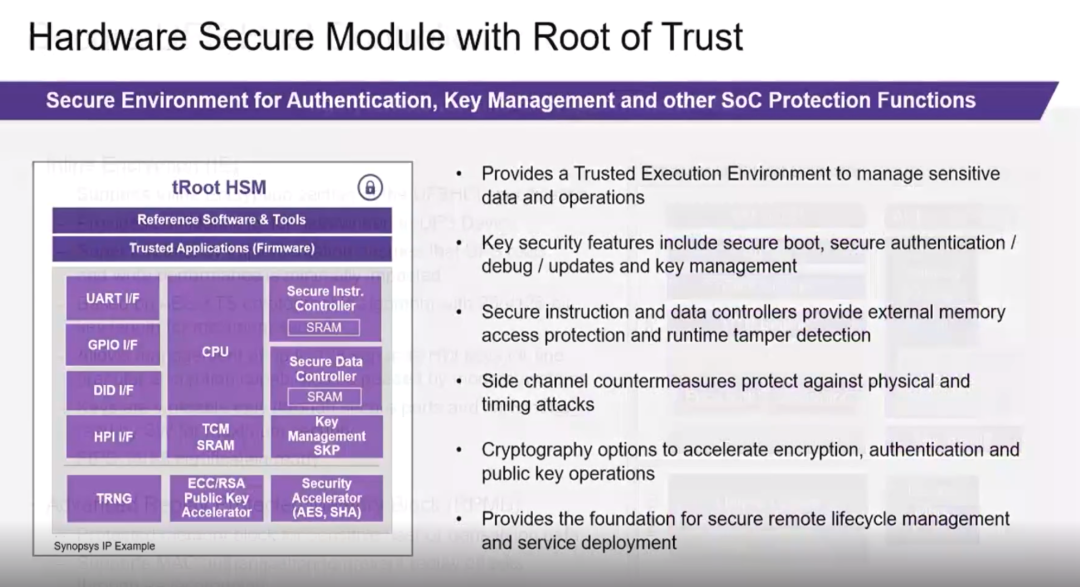

除了建立芯片接口安全的兩個核心要素:設備認證、密鑰管理以及數據完整性和機密性保護之外,可信執行環境的建立也是一個潛在的基礎要求。

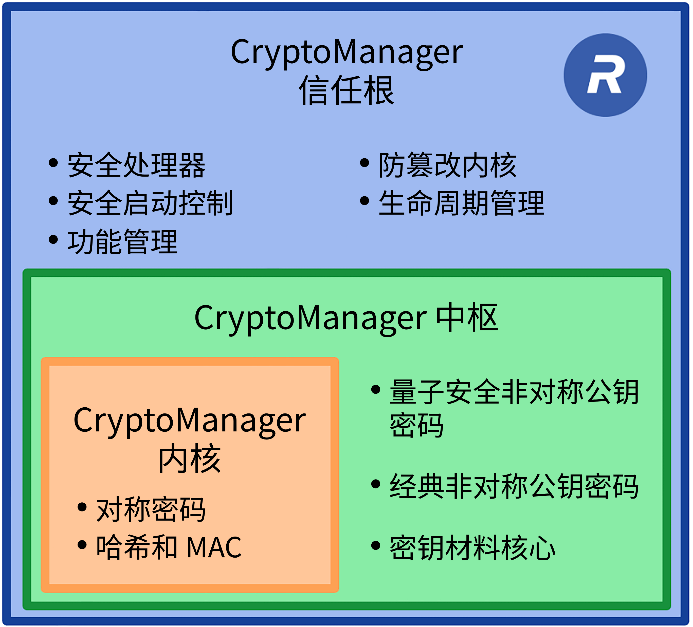

從芯片或者是系統安全的設計角度來講,希望保護從靜態存儲到上電啟動,再到運行階段的數據和服務的訪問等不同階段的數據安全。針對這一功能,新思科技為開發者提供了tRoot HSM硬件安全模塊。如上圖所示,作為一個可編程的安全子系統,該模塊內嵌了密碼算法的硬件加速器和可擴展的外設接口,非常適合作為芯片當中的安全中樞,為其他的接口安全功能提供必要的可信執行環境的支持。

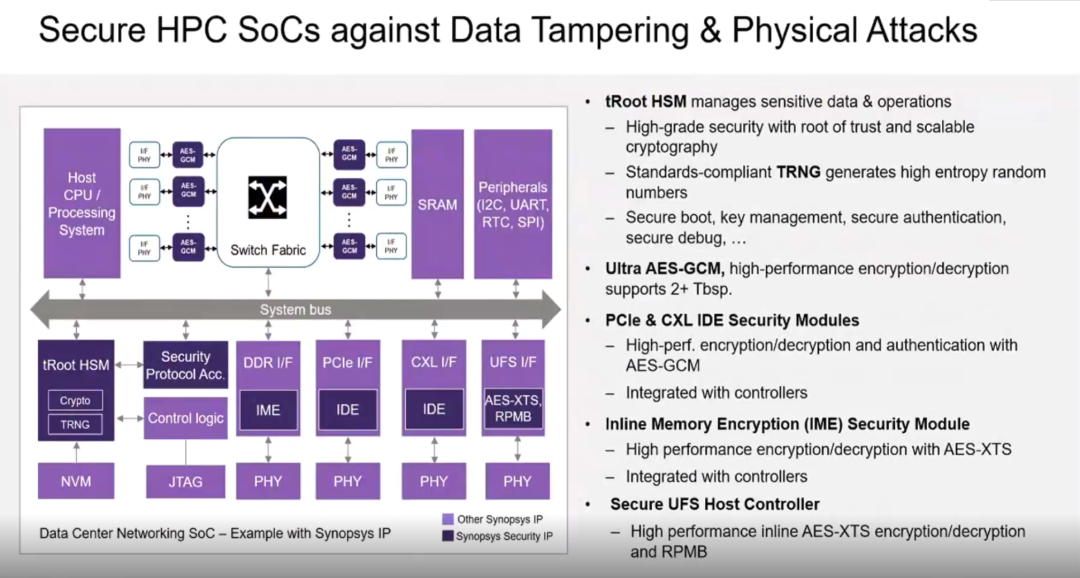

綜合來看,新思科技的各種接口與安全相融合的設計理念正在被越來越多的芯片廠商和開發者所認可和采納。從下圖所示的SoC架構來看,其中淺紫色的部分是新思科技可以提供的各種IP解決方案,深紫色的部分則是他們在信息安全方面的解決方案。

其中,tRoot HSM扮演一個security manager的角色,作為一個硬件隔離的可執行單元,可以部署到SoC當中來掌控從安全啟動、密鑰管理到鑒權認證等不同階段的任務,并且為其他分立的接口安全模塊提供管理。

此外,除了上述提到的接口安全IP,針對尚未形成統一安全標準的其他接口,新思科技還可以提供一些獨立的高性能密碼算法和協議加速器來把密碼算法和接口傳輸解耦合,來靈活的支持不同接口的傳輸技術和業務場景。

“

結語

隨著技術的進步,高性能計算逐漸被應用在更廣泛的領域,例如AI、機器學習、大數據分析、云端計算及網絡通信等。高算力的發展及高性能計算的突破,成為支撐數字化世界的重要推手。

在這個過程中,大數據量、高吞吐率、低延遲的特性使得各種高速接口技術在芯片設計當中被廣泛地部署。其中,數據作為核心要素,其安全性越發受到整個行業的普遍重視,已成為一個類似于性能、面積、功耗等傳統指標的重要評估要素。

因此,為了進一步保護高性能接口的數據安全,需要在鑒權、數據完整性、機密性以及可信執行環境方面去尋求相應的解決方案,同時滿足高性能計算在吞吐率和延遲方面的一些要求。

作為行業領先的方案供應商,新思科技致力于通過自主研發先進工藝芯片IP產品,響應高性能計算時代接口安全的發展新趨勢,全面賦能芯片設計,通過提供包括PCIe、CXL、DDR、UFS等豐富的集成數據安全保護模塊的接口IP,更好的幫助開發者應對接口安全和系統安全方面的需求和挑戰。

審核編輯 :李倩

-

接口

+關注

關注

33文章

9520瀏覽量

157032 -

IP

+關注

關注

5文章

1863瀏覽量

155844 -

數據安全

+關注

關注

2文章

768瀏覽量

30852

原文標題:如何通過接口IP來保障芯片數據安全?

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

電能質量在線監測裝置的權限管理如何保障數據安全?

硬件加密引擎在保障數據安全方面有哪些優勢呢?

芯源半導體安全芯片技術原理

通過sysmem接口擴展內存空間

VPP加密芯片撐起虛擬電廠安全

如何保障遠程運維過程中的數據安全和隱私?

芯動科技全套IP通過ISO 26262汽車功能安全最高等級認證

NVMe控制器IP設計之接口轉換

AI應用激增,硬件安全防護更關鍵,Rambus 發布CryptoManager安全IP解決方案

Rambus 通過新一代CryptoManager安全IP解決方案增強數據中心與人工智能保護

如何通過接口IP來保障芯片數據安全?

如何通過接口IP來保障芯片數據安全?

評論