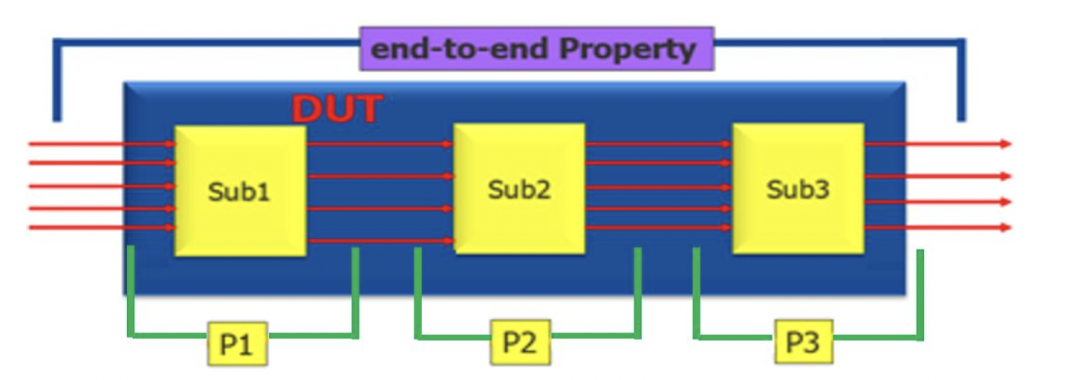

分解一個(gè)復(fù)雜端到端斷言屬性的一種方法是基于模塊化分級(jí)斷言證明,如下圖所示:

端到端屬性被分解為分別驗(yàn)證每個(gè)子模塊:

P1 驗(yàn)證 Sub1

P2 驗(yàn)證 Sub2

P3 驗(yàn)證 Sub3

我們使用P1已證明的屬性作為P2斷言證明的假設(shè),所以模塊化分級(jí)證明的要點(diǎn)就在于“后級(jí)模塊的證明假設(shè),一定要有前級(jí)斷言的證明保證”,即“assume-guarantee”原則,這個(gè)原則在EDA仿真驗(yàn)證環(huán)境集成時(shí)也是適用的。

由于這種“assume-guarantee”原則的保證,上面3個(gè)模塊如果都完成了證明,那么也相當(dāng)于端到端的斷言屬性完成了證明。

分而治之,各個(gè)擊破的方法,在大規(guī)模芯片驗(yàn)證中非常適用,但是也很容易引入質(zhì)量風(fēng)險(xiǎn)。

審核編輯:劉清

-

eda

+關(guān)注

關(guān)注

72文章

3113瀏覽量

182921 -

EDA仿真技術(shù)

+關(guān)注

關(guān)注

0文章

5瀏覽量

5564

原文標(biāo)題:如何降低Formal assertion的復(fù)雜性(二)

文章出處:【微信號(hào):芯片驗(yàn)證工程師,微信公眾號(hào):芯片驗(yàn)證工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

怎樣去降低H.264 INTRA幀編碼的運(yùn)算復(fù)雜性和存儲(chǔ)器需求?

如何用可重構(gòu)射頻前端簡(jiǎn)化LTE設(shè)計(jì)復(fù)雜性?

如何去降低H.264 INTRA幀編碼的運(yùn)算復(fù)雜性?

Intersil推出60V創(chuàng)新同步降壓控制器,大幅降低電源設(shè)計(jì)復(fù)雜性和系統(tǒng)成本

基于構(gòu)件回歸測(cè)試的復(fù)雜性度量框架

如何降低人工智能的復(fù)雜性

大數(shù)據(jù)分析學(xué)習(xí)的挑戰(zhàn):復(fù)雜性、不確定性及涌現(xiàn)性

降低無(wú)線連接、共存的復(fù)雜性

可以通過(guò)降低約束的復(fù)雜度來(lái)優(yōu)化Formal的執(zhí)行效率嗎?

Formal Verification的基礎(chǔ)知識(shí)

使用Emulex SAN管理器降低操作復(fù)雜性

如何降低Formal assertion的復(fù)雜性呢?

如何降低Formal assertion的復(fù)雜性呢?

評(píng)論