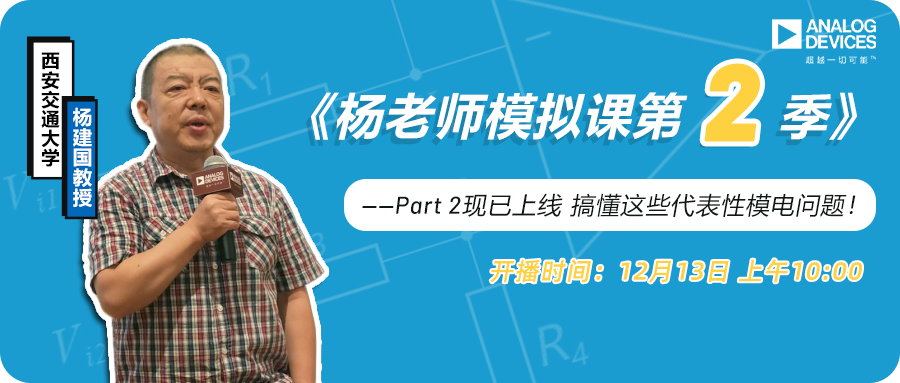

圖1. 典型測量信號鏈

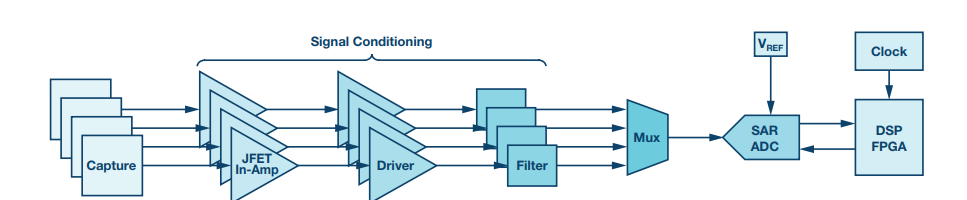

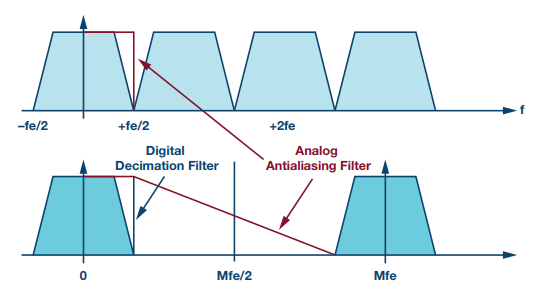

圖2.通過添加數字抽取濾波器比較頻譜噪聲密度

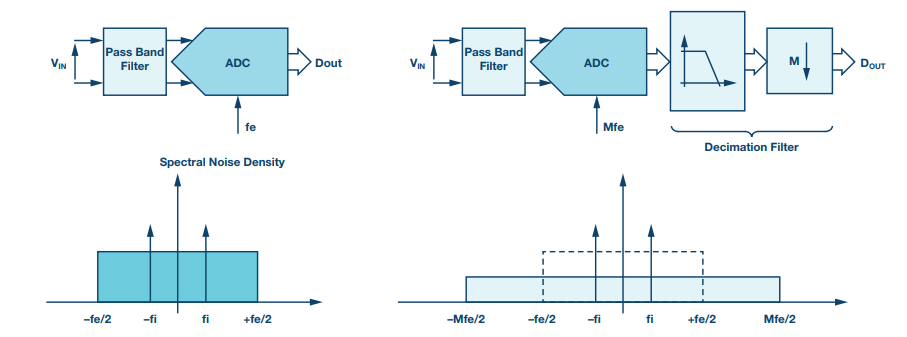

以高于奈奎斯特定理要求的最小值的FSE速率對信號進行采樣,可以通過處理和增加編碼器的信噪比來執行增益運算,并因此增加有效位的數量。實際上,量化噪聲和熱噪聲被同化為白噪聲,該噪聲在整個奈奎斯特頻帶及以外均勻分布。過采樣之后,通過濾波和嚴格以最小所需采樣速率(或2×BW)限制有用頻帶,頻帶每降低一個倍頻程,噪聲能量將降低3dB,如圖2所示。換句話說,過采樣因子為4時最為理想,在理論上使信噪比增加了6dB;即是說,增加了一位,如等式1所示:

圖3.過采樣分布在-3dB條件下截止頻率與阻帶起點之間的過渡帶

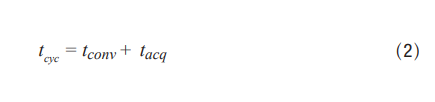

故定義最大采樣頻率,其構成為:

其本身由輸出數據的讀取速率調理,其中,

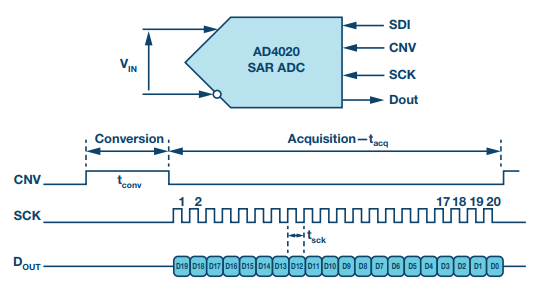

圖4.AD4020的時序圖

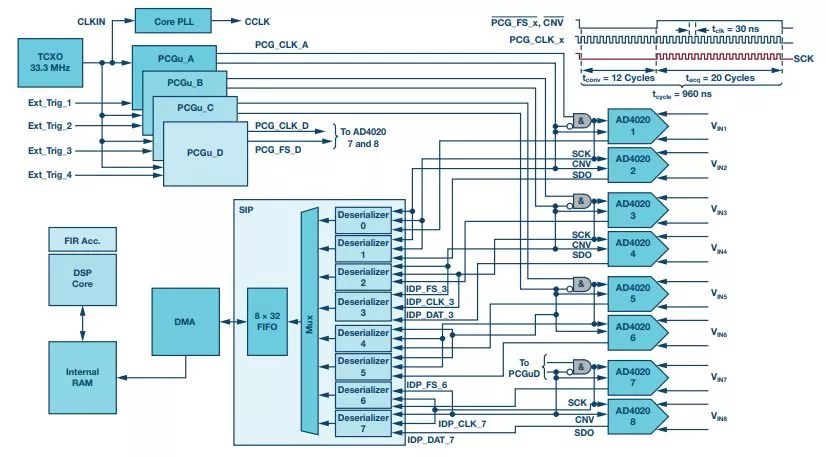

圖5.通過解串行將8個20位1MSPSSAR ADC接入SHARC DSP;DMA數據傳輸進DSP內部RAM

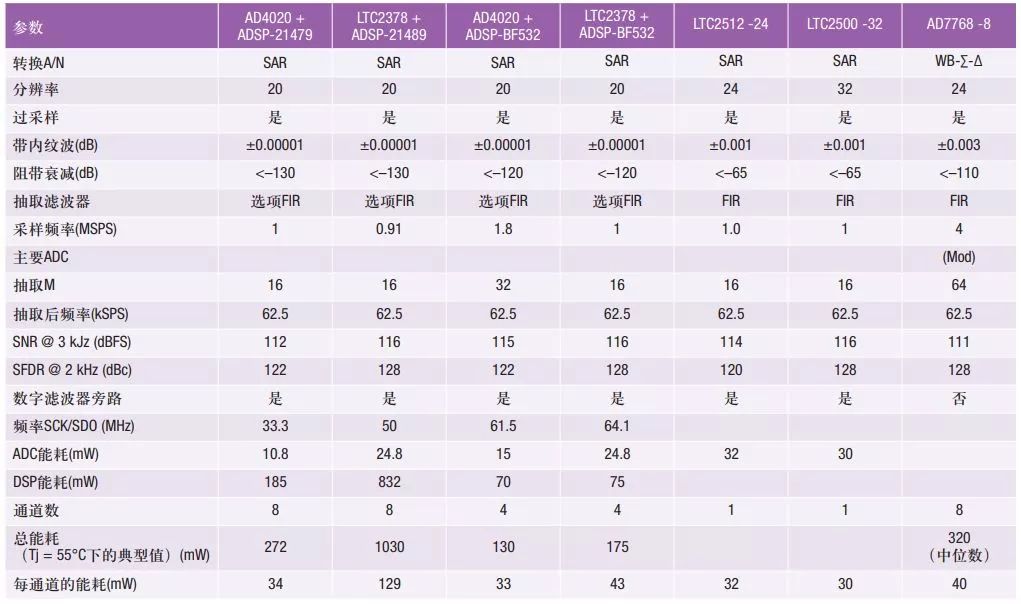

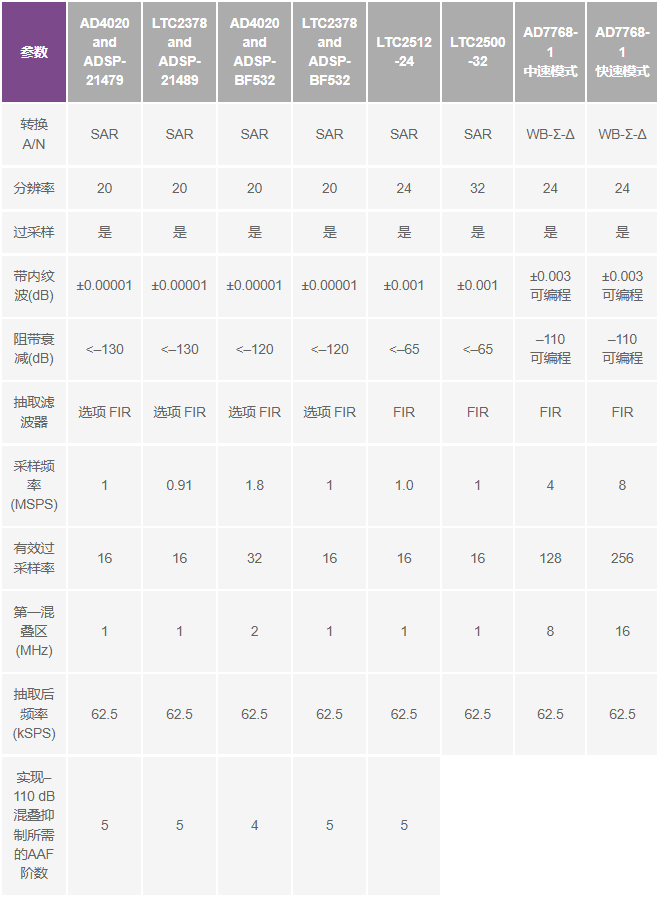

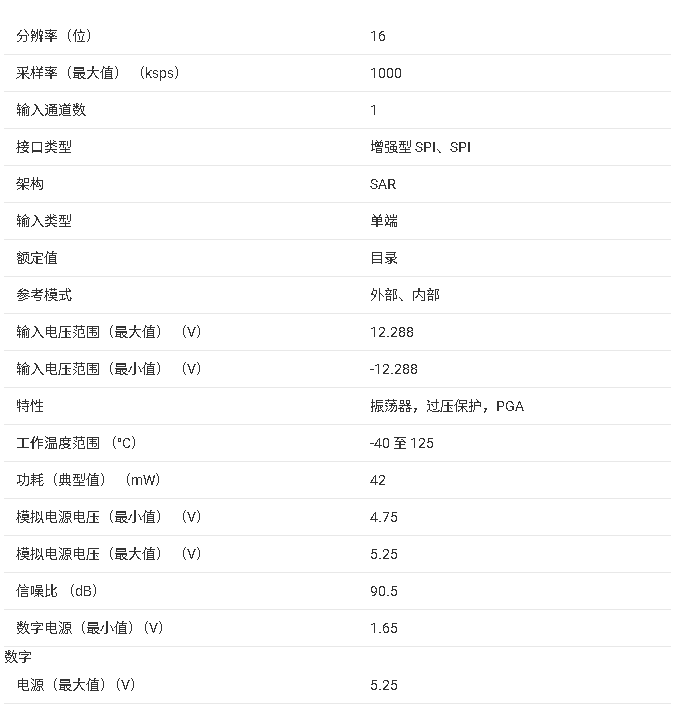

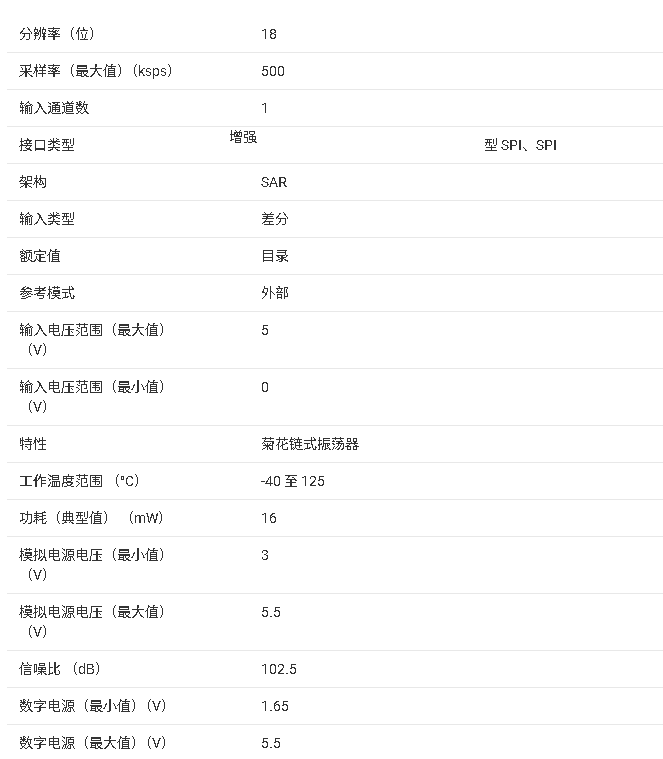

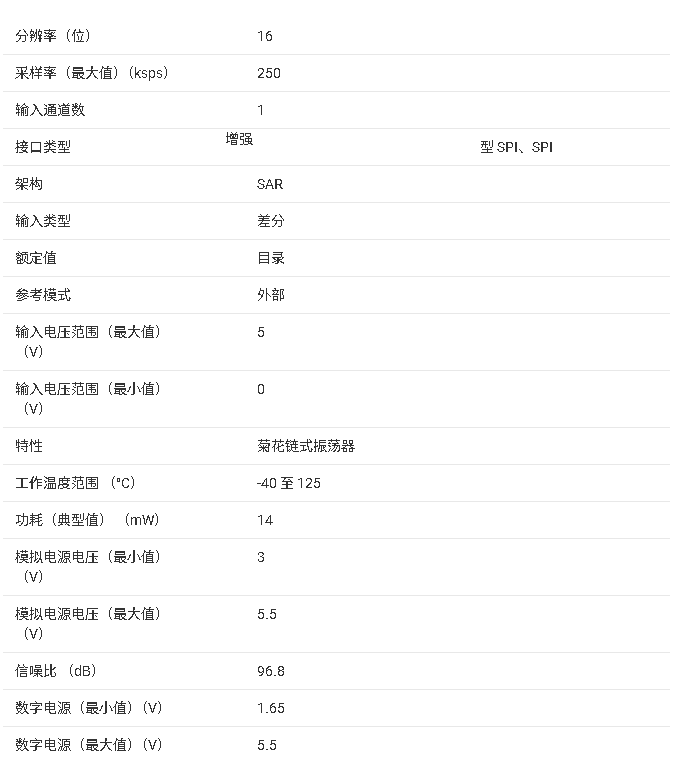

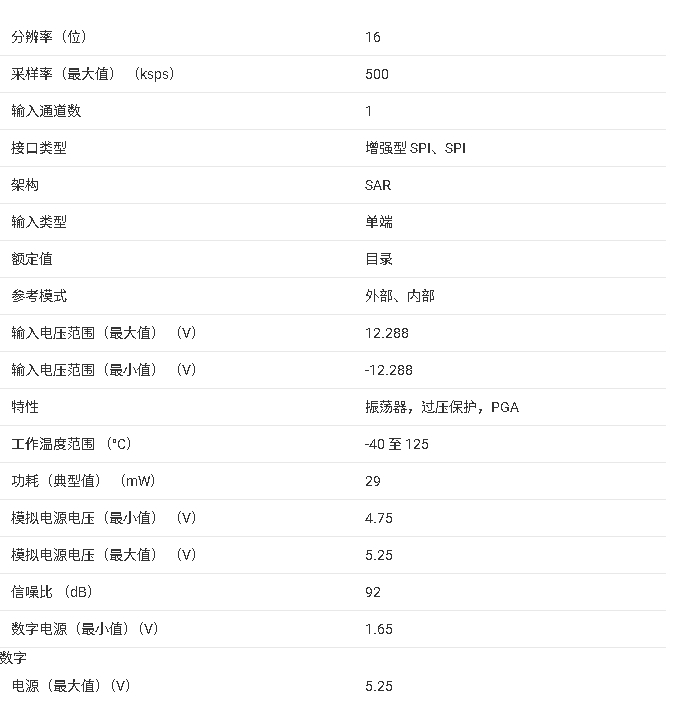

表1.不同SAR ADC與DSP相比的情況對比

抽取專用直接或優化FIR濾波器

級聯多速率FIR濾波器(1/2頻段)

多相FIR濾波器

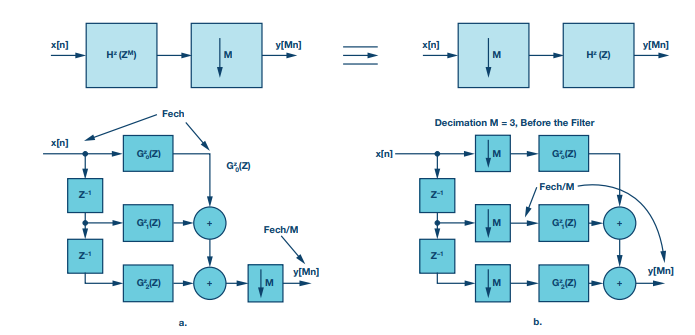

無論是FIR還是IIR類型的多相濾波器都是抽取或插值濾波器最有效的實現方案之一。然而,傳統數字處理方案要求在抽取之前進行濾波。在此假設下,1/M抽取濾波器由低通濾波器和緊隨其后的采樣頻率降級組成(圖6a)。預先對信號濾波,避免頻譜混疊,然后以M-1的速率定期消除樣本。然而,常規FIR或其他結構針對這些抽取濾波器的直接實現方案存在資源浪費問題,因為被拒樣本是幾十甚至幾百次累乘(MAC)的結果。使用分解成若干濾波器組的多相濾波器或是針對抽取進行優化的濾波器,可以基于某些特點(如圖6b所示)形成高效的濾波器。

圖6a和6b.常規抽取濾波器和采用多相方案的抽取濾波器

支持IEEE-754定點或浮點32位算術格式?

有四個并行運行的累乘單元?

支持單速率和多速率處理模式(抽取或插值)?

一次簡單迭代可以處理最多32個FIR濾波器,總共多達1024個系數

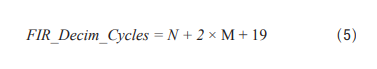

N為濾波器的系數的個數,M為抽取速率。

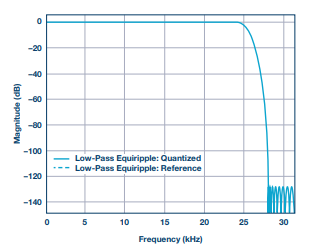

圖7.抽取濾波器的濾波器響應

表1. 不同SAR ADC與DSP相比的情況對比

原文標題:高精度 SAR ADC的抗混疊濾波考慮因素

文章出處:【微信公眾號:亞德諾半導體】歡迎添加關注!文章轉載請注明出處。

-

亞德諾

+關注

關注

6文章

4680瀏覽量

16698

原文標題:高精度 SAR ADC的抗混疊濾波考慮因素

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

泡沫起升儀模擬前端設計:微弱信號放大與抗混疊濾波電路

模數轉換器(ADC)的最高使用頻段取決于哪些因素

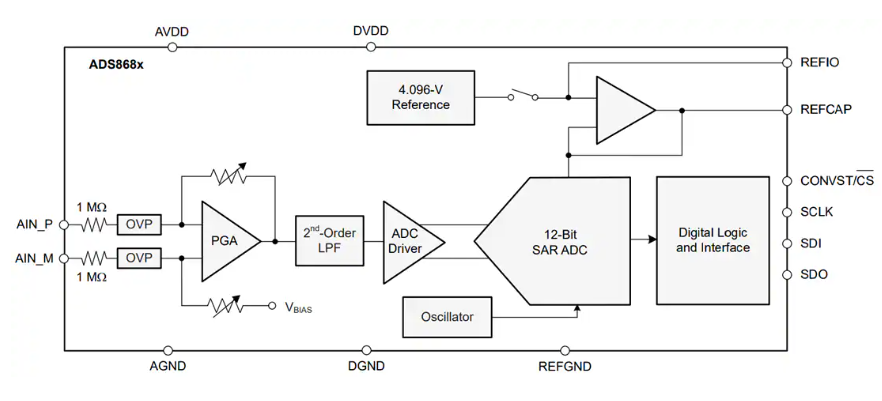

ADS868x 16 位高速單電源 SAR ADC 核心信息總結

ADS891xB 系列 18 位高精度 SAR ADC 核心信息總結

ADS892xB 系列 16 位高精度 SAR ADC 核心信息總結

ADS8685 16位、500kSPS、1通道SAR ADC技術手冊

高速adc,類比高精度ADC芯片ADX3202AQFN32詳解

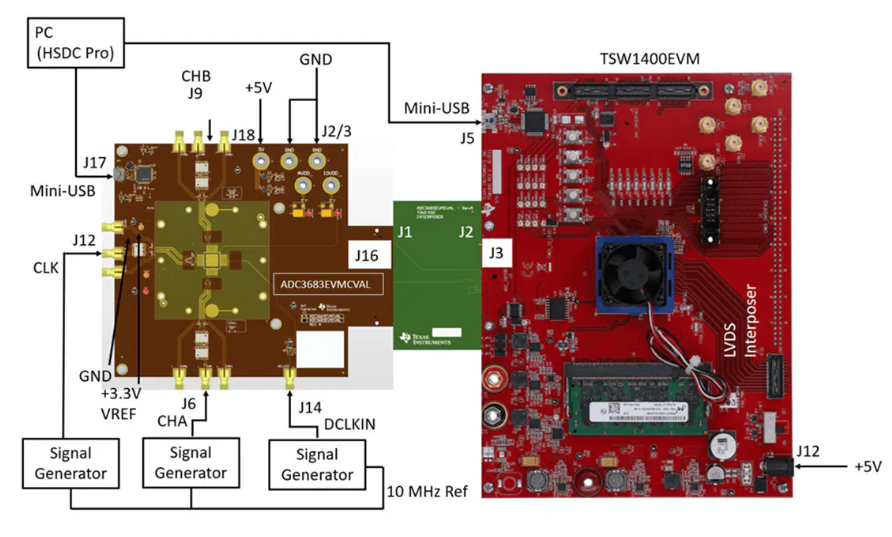

ADC3683EVMCVAL評估模塊技術解析與應用指南

笙泉高精度24位ADC (MAD2402)新上市,賦能精準量測

Texas Instruments ADS8661W 12位高速SAR ADC數據手冊

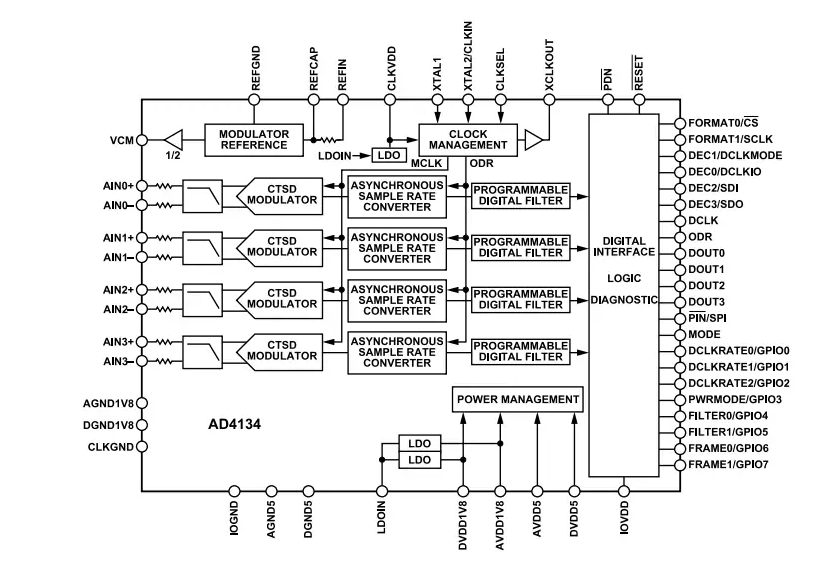

Analog Devices Inc. AD4134四通道模數轉換器數據手冊

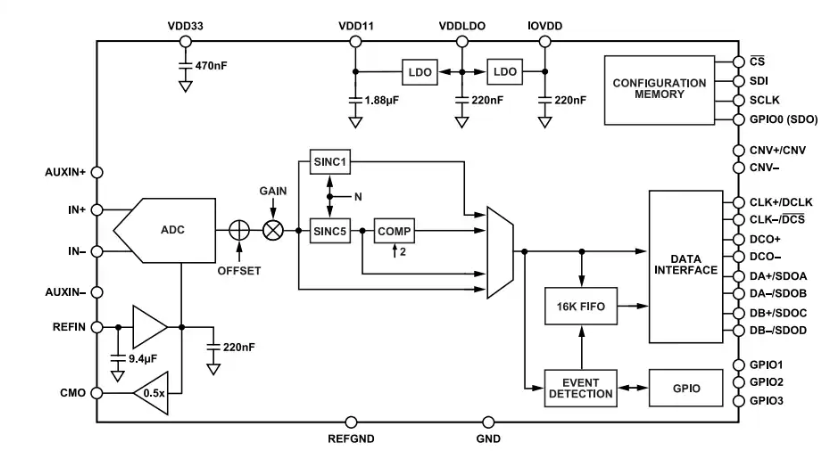

Analog Devices Inc. AD4080差分SAR ADC數據手冊

高精度 SAR ADC的抗混疊濾波考慮因素

高精度 SAR ADC的抗混疊濾波考慮因素

評論