單片機或者FPGA給SPI控制信號給到鎖相環芯片時,經常要串接一個22ohm或者33ohm的電阻,這是有啥道理呢?

阻抗不連續,會引起電磁波反射,而反射又會引起信號的失真。所以在進行高速數字電路設計時,經常也會涉及到匹配。但是,這個匹配和射頻上的匹配,在操作上有所不同。

射頻上的匹配一般都是用電感電容來減小反射,但是數字電路中,則一般用電阻來進行匹配。

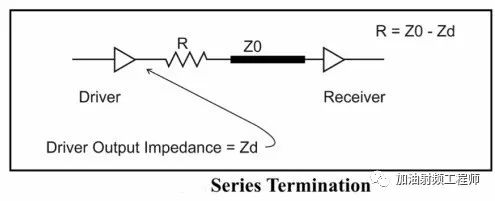

在數字電路中,源端匹配是匹配方式中的一種。而以上提到的,在通路中串接電阻,即是典型的源端匹配。假設數字電路的輸出電阻為Zd,傳輸線的特性阻抗為Z0,則串聯的電阻R=Zo-Zd。

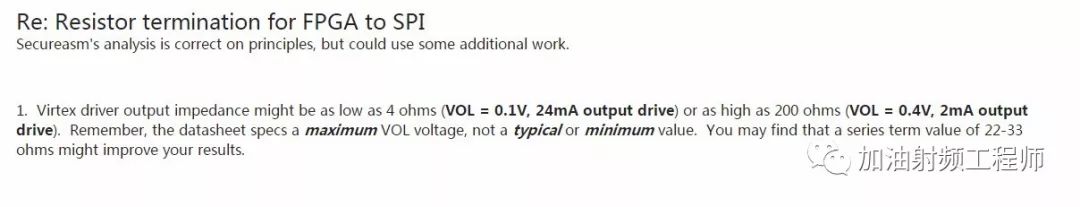

論壇上(1)有提到通過Zo = (Vdd-VOH) / IOH以及Zo = VOL/IOL來計算數字電路的輸出電阻。但是實際操作時,并不是這么理想。

如(2)中所述,即使對于同一型號器件,值也會有很大區別。

所以實際操作的時候,可以在電路上留個位置,邊更換電阻阻值,邊用示波器測試,看什么時候波形的振鈴消失。

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

電阻

+關注

關注

88文章

5781瀏覽量

179524 -

單片機

+關注

關注

6076文章

45495瀏覽量

670367 -

阻抗

+關注

關注

17文章

988瀏覽量

49238 -

SPI

+關注

關注

17文章

1885瀏覽量

101246 -

控制信號

+關注

關注

0文章

200瀏覽量

12693

原文標題:為什么SPI等信號輸出信號要加一個22或者33ohm的電阻呢

文章出處:【微信號:加油射頻工程師,微信公眾號:加油射頻工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

關于LVPECL時鐘信號的的疑問

本人遇到一個問題如下芯片的pcie的參考時鐘要求hcsl或者lvpecl電平,芯片內部存在onchip AC耦合電容在時鐘發出端,p&N分別下拉150ohm至gnd之后 ,

發表于 03-05 23:58

為什么SPI沒有輸出信號?

我試圖讓我的dspic33ep512mc202通過DMAi進行SPI,使用XC16編譯器和MCC生成我的代碼。這是我的代碼,所以SPI沒有輸出信號

發表于 11-07 09:08

如何準確測試75 Ohm系統的信號

。也就是說,50 Ohm特征阻抗對應的功率容量和衰減性能都不是最佳的。單論衰減性能,75 Ohm特征阻抗要比50 Ohm低不少,但是其應用領域比較專一,主要應用于廣播、電視

發表于 09-02 14:12

?1193次閱讀

SPI輸出信號要加22或者33歐姆電阻的原因

阻抗不連續,會引起電磁波反射,而反射又會引起信號的失真。所以在進行高速數字電路設計時,經常也會涉及到匹配。但是,這個匹配和射頻上的匹配,在操作上有所不同。

為什么高頻信號不能直接通過電阻的分壓來實現信號的衰減呢?

用于通信、雷達、醫療等領域。但是,與低頻信號相比,高頻信號容易衰減,這是為什么呢?為什么高頻信號不能直接通過

為什么SPI等信號輸出信號要加一個22或者33ohm的電阻呢

為什么SPI等信號輸出信號要加一個22或者33ohm的電阻呢

評論