本文主要闡述了在電力電子電路應(yīng)用中,為什么需要驅(qū)動(dòng)芯片并聯(lián)使用,芯片能夠并聯(lián)使用應(yīng)具備什么特征,以及驅(qū)動(dòng)芯片并聯(lián)使用應(yīng)注意的問(wèn)題點(diǎn)。

01

驅(qū)動(dòng)芯片與功率管的配合

功率器件在工業(yè)、能源、汽車等應(yīng)用中被廣泛的使用以實(shí)現(xiàn)各種的功率變換,同時(shí)隨著社會(huì)的迅速發(fā)展,功率變換的功率等級(jí)也越來(lái)越高。在大功率的功率因數(shù)校正電路 (PFC),低壓大電流的同步整流電路中, 往往需要多個(gè)功率管并聯(lián)以滿足電路功率輸出的需求。

多個(gè)功率管并聯(lián),導(dǎo)致功率管的QGC,QGE變大,若選用驅(qū)動(dòng)芯片的驅(qū)動(dòng)電流較小,則功率管開(kāi)通時(shí)間很長(zhǎng),此時(shí)會(huì)導(dǎo)致功率管損耗很大,發(fā)熱嚴(yán)重。驅(qū)動(dòng)輸出進(jìn)行并聯(lián)來(lái)驅(qū)動(dòng)功率管是一種解決方案。

02

驅(qū)動(dòng)芯片并聯(lián)使用

如上述所,當(dāng)功率管的門極電荷比較大,而驅(qū)動(dòng)芯片能力不足時(shí),為了選擇合適的開(kāi)關(guān)速度和性能,需要將驅(qū)動(dòng)芯片輸出端并聯(lián)使用。

但驅(qū)動(dòng)芯片并聯(lián)時(shí),對(duì)驅(qū)動(dòng)芯片要求較高,并不是所有的驅(qū)動(dòng)芯片都適合并聯(lián)使用。

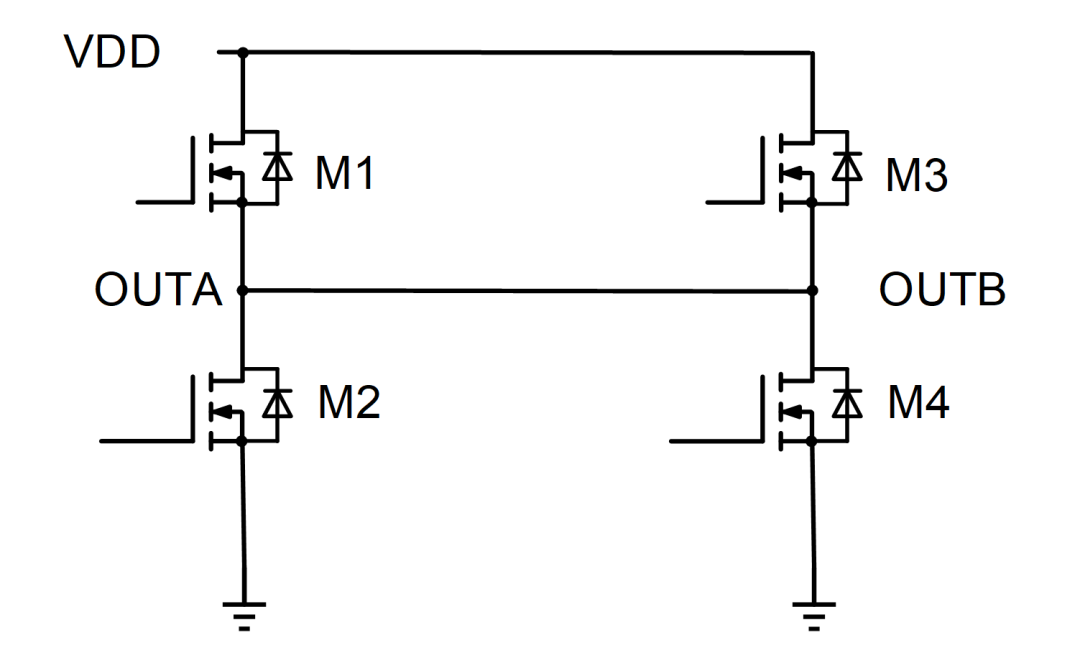

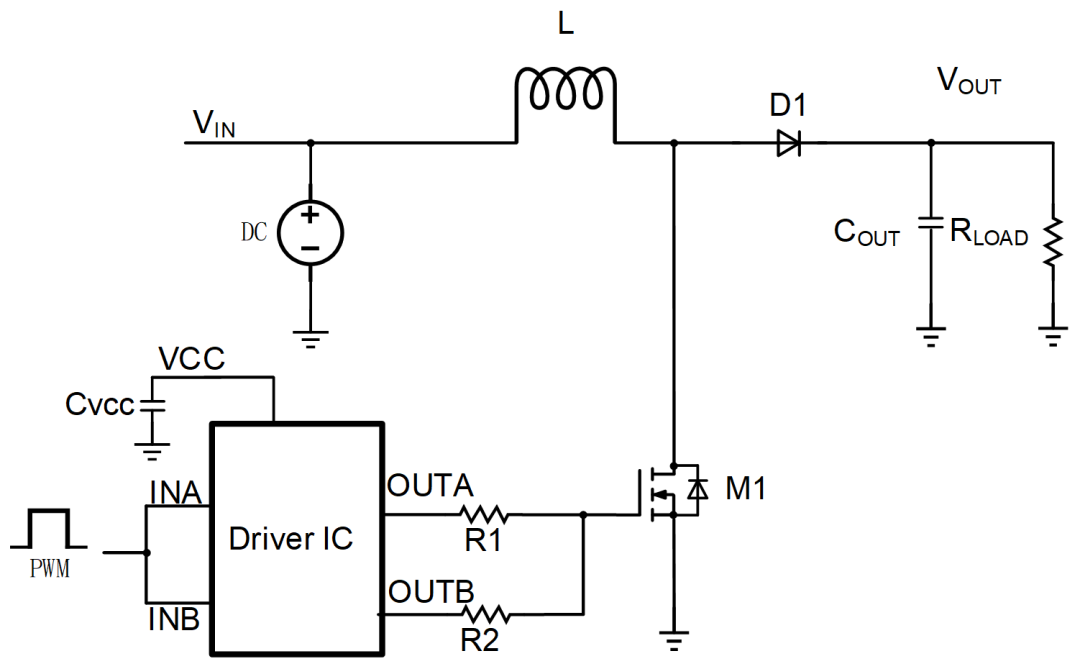

圖1.顯示了驅(qū)動(dòng)芯片并聯(lián)使用時(shí)的示意圖。由于是并聯(lián)使用,要求內(nèi)部的MOSFET M1與M3,M2與M4同時(shí)開(kāi)通,同時(shí)關(guān)斷,否則OUTA與OUTB之間必然存在電位差,導(dǎo)致M1與M4或者M(jìn)2與M3同時(shí)導(dǎo)通,從而導(dǎo)致共通的現(xiàn)象而損壞驅(qū)動(dòng)芯片。

圖 1. 驅(qū)動(dòng)芯片并聯(lián)使用示意圖

因此,在驅(qū)動(dòng)芯片并聯(lián)的應(yīng)用中需要特別關(guān)注以下幾點(diǎn):

(1)驅(qū)動(dòng)芯片本身的對(duì)稱問(wèn)題。兩個(gè)驅(qū)動(dòng)通道的參數(shù)要一致,每路驅(qū)動(dòng)的輸入到輸出的延時(shí)、輸入的翻轉(zhuǎn)電平以及輸出的上升、下降時(shí)間要一致。

(2)兩路輸入信號(hào)的短接點(diǎn)要盡量靠近芯片的管腳,并且輸入信號(hào)要有快速的dv/dt。

(3)芯片的外圍應(yīng)用電路上,可以在外部增加一個(gè)電阻,用來(lái)限制直通電流。

下面以SLM27524芯片為例來(lái)說(shuō)明驅(qū)動(dòng)并聯(lián)應(yīng)用中要注意的一些問(wèn)題。

03

驅(qū)動(dòng)芯片的一致性

驅(qū)動(dòng)芯片并聯(lián)對(duì)芯片本身的一致性是有要求的,如果兩路驅(qū)動(dòng)的一致性不好,在并聯(lián)時(shí)會(huì)導(dǎo)致驅(qū)動(dòng)芯片的損壞。SLM27524在設(shè)計(jì)的時(shí)候已經(jīng)考慮了這種并聯(lián)應(yīng)用的需求,因此在兩路驅(qū)動(dòng)的延時(shí)上做了比較好的匹配。

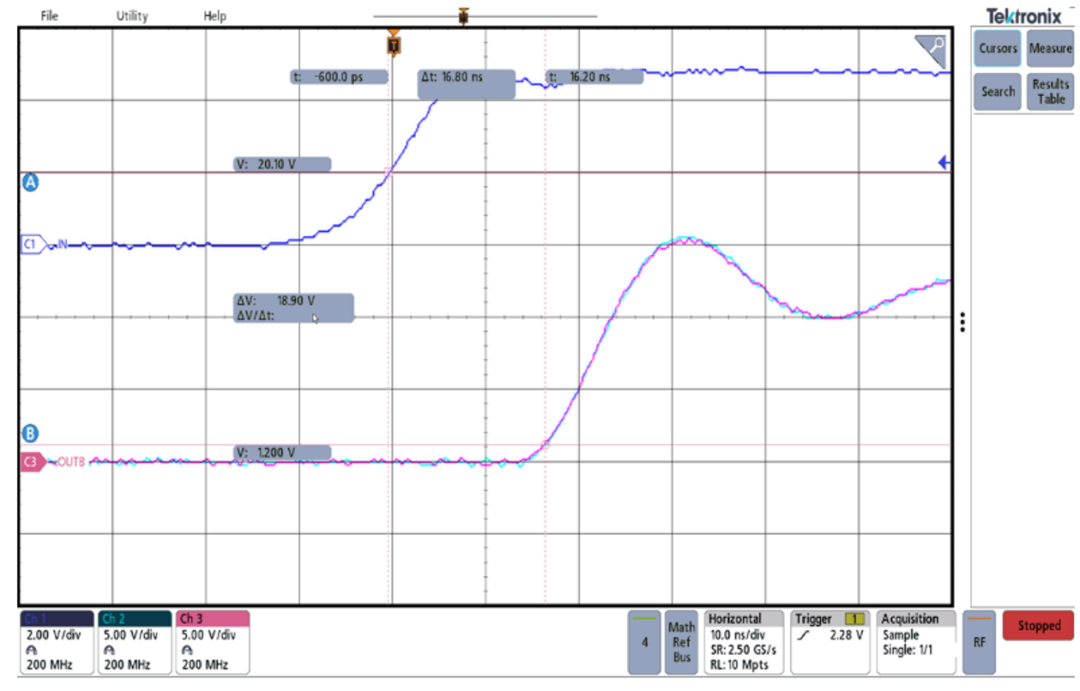

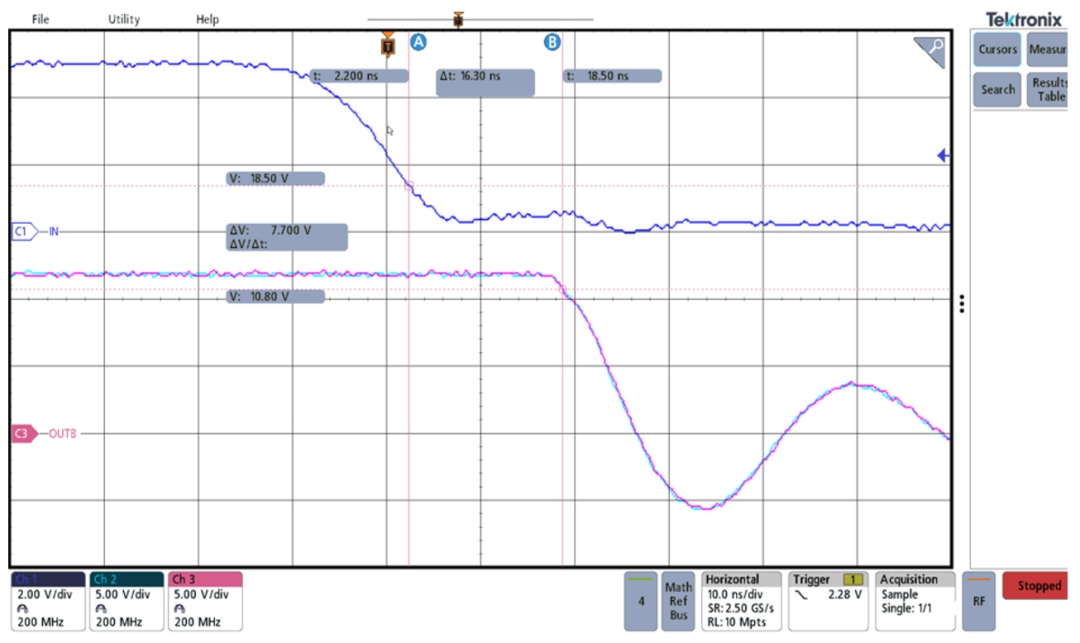

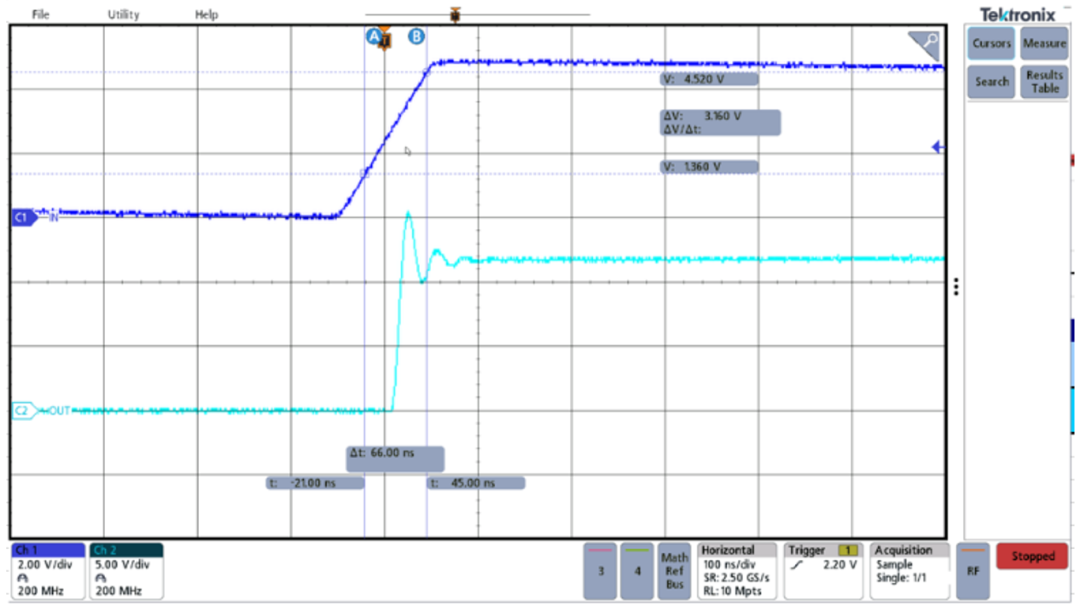

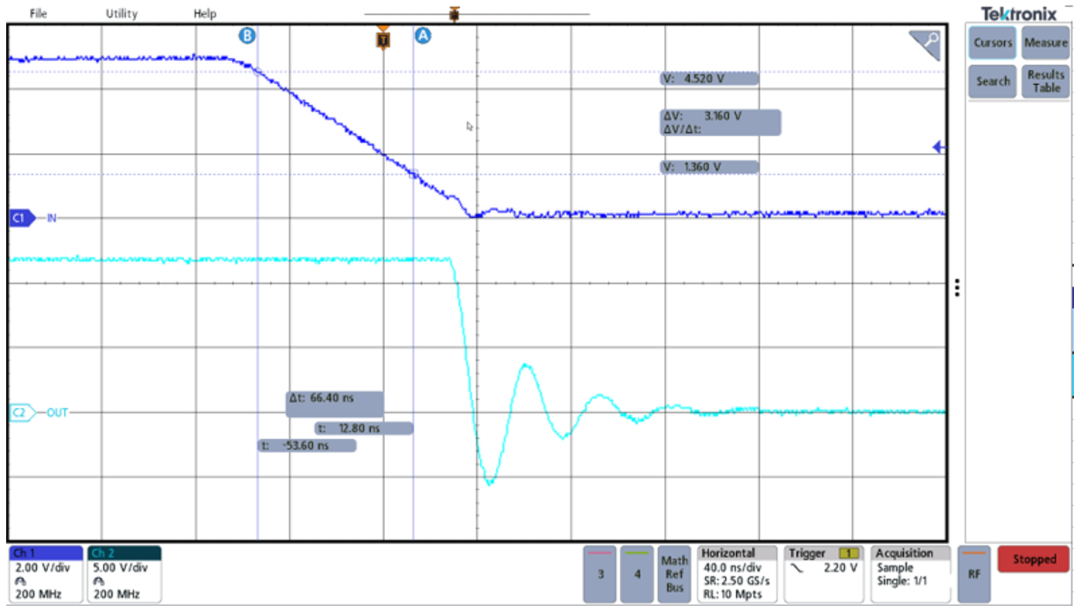

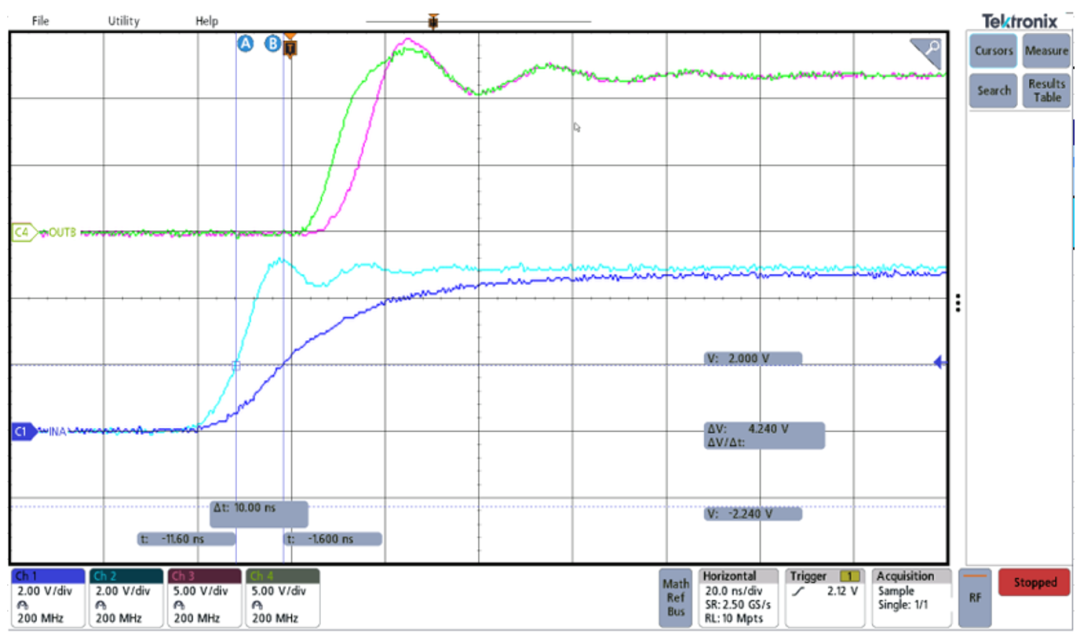

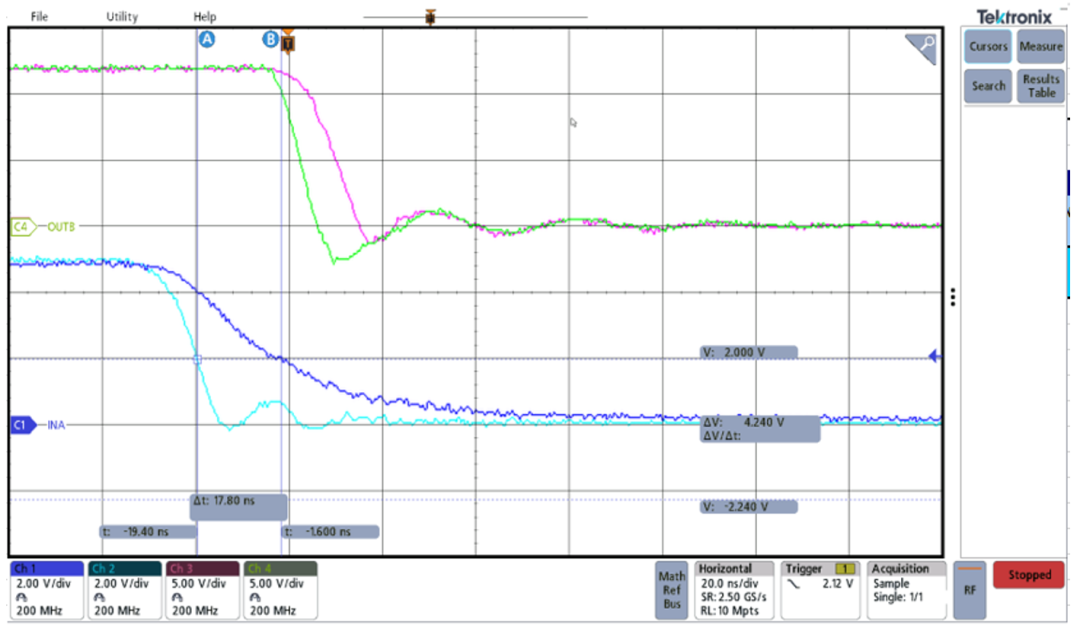

圖2和圖3顯示了SLM27524在給同一個(gè)輸入信號(hào)時(shí),兩路驅(qū)動(dòng)輸出在開(kāi)通、關(guān)斷時(shí)的波形。從波形測(cè)試上看,SLM27524的兩路驅(qū)動(dòng)在開(kāi)通延時(shí)、關(guān)斷延時(shí)、上升時(shí)間和下降時(shí)間上都有很好的一致性。

圖 2. SLM27524通道開(kāi)通時(shí)的波形

CH1: 驅(qū)動(dòng)輸人IN 丨 CH2: 驅(qū)動(dòng)輸出OUTA

CH3: 驅(qū)動(dòng)輸出OUTB

圖 3. SLM27524通道關(guān)斷時(shí)的波形

CH1: 驅(qū)動(dòng)輸人IN 丨 CH2: 驅(qū)動(dòng)輸出OUTA

CH3: 驅(qū)動(dòng)輸出OUTB

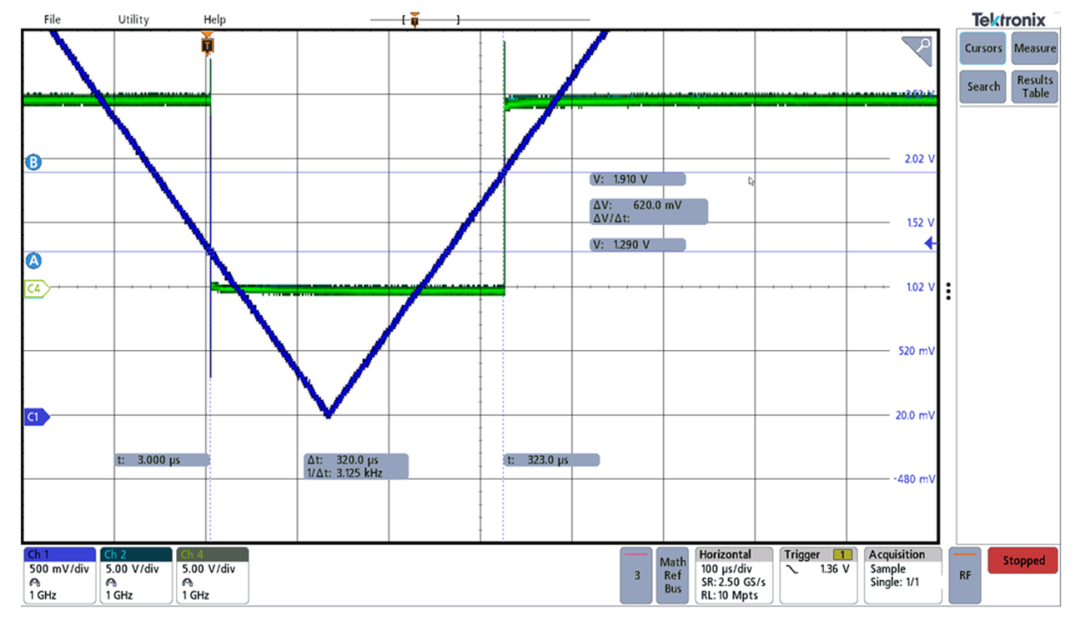

圖4顯示了SLM27524兩個(gè)通道的輸入閾值。從測(cè)試的波形上看,兩個(gè)通道的輸入閾值是一致的。

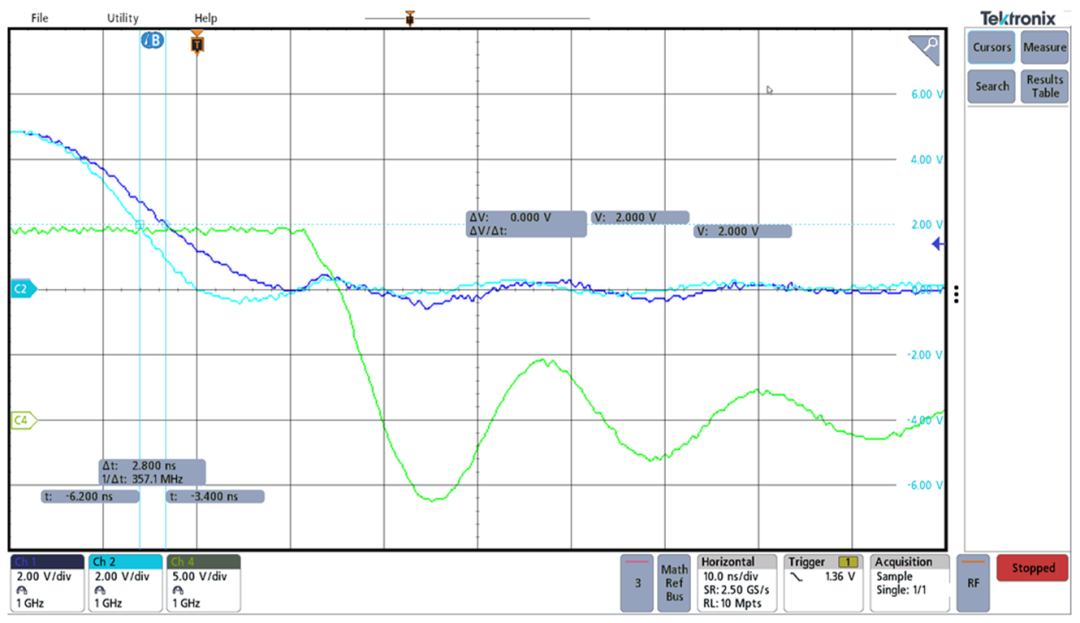

圖 4. SLM27524 輸入閾值門限波形

CH1: 驅(qū)動(dòng)輸人IN 丨 CH2: 驅(qū)動(dòng)輸出OUTA

CH4: 驅(qū)動(dòng)輸出OUTB

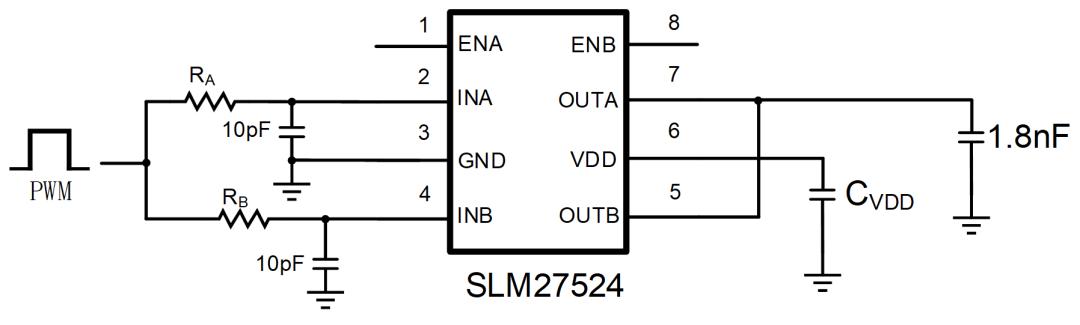

為了驗(yàn)證SLM27524兩個(gè)通道直接并聯(lián)應(yīng)用的有效性,人為在兩路輸入信號(hào)上加入延時(shí),并按下圖5進(jìn)行試驗(yàn)。當(dāng)改變電阻RA、RB的阻值時(shí),就改變了通道A、B之間的輸入時(shí)間差。

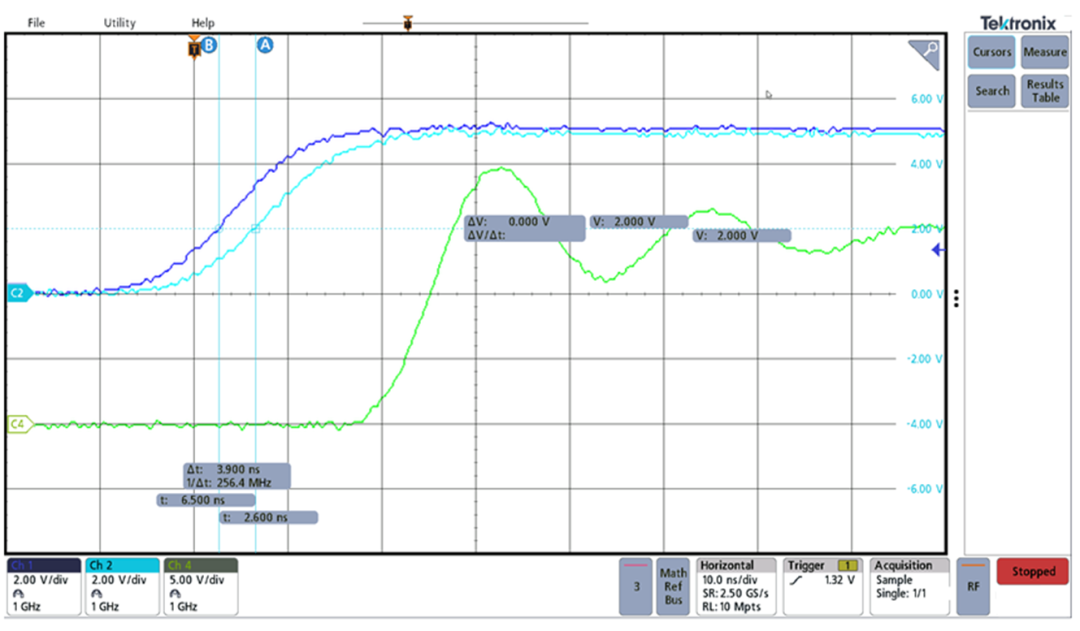

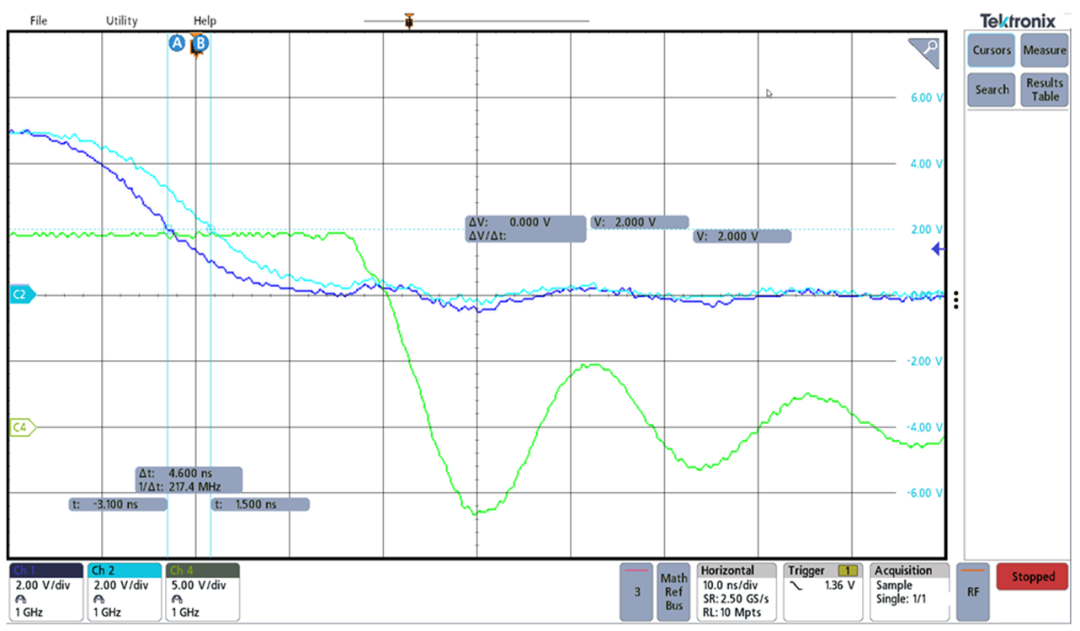

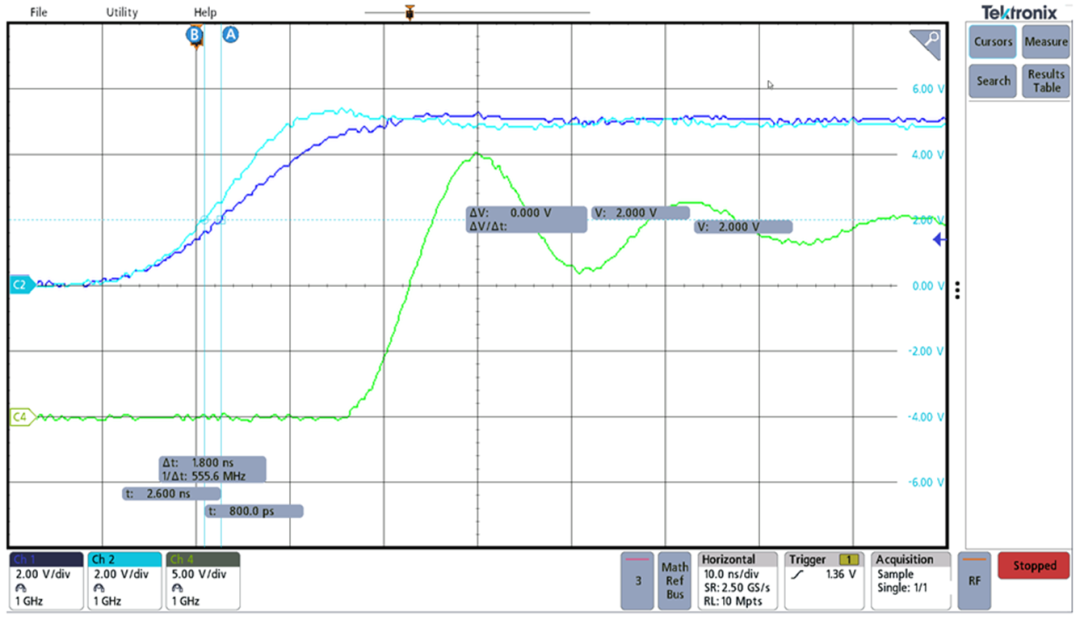

圖6到圖9顯示了通道A和通道B在不同的輸入延時(shí)情況下的輸出波形。

在一定輸入延時(shí)差范圍內(nèi),無(wú)論是INA超前還是滯后INB,芯片直接并聯(lián)仍然正常輸出波形。這說(shuō)明SLM27524具有較強(qiáng)的魯棒性,能夠容忍一定程度的輸入信號(hào)延時(shí)差。

圖 5. SLM27524并聯(lián)魯棒試驗(yàn)電路

圖 6. SLM27524 INA超前INB 3.9ns并聯(lián)波形

CH1: 驅(qū)動(dòng)輸人INA 丨 CH2: 驅(qū)動(dòng)輸入INB

CH4:驅(qū)動(dòng)輸出OUT

圖 7. SLM27524 INA超前INB 4.6ns并聯(lián)波形

CH1: 驅(qū)動(dòng)輸人INA 丨 CH2: 驅(qū)動(dòng)輸入INB

CH4:驅(qū)動(dòng)輸出OUT

圖 8. SLM27524 INA滯后INB 1.8ns并聯(lián)波形

CH1: 驅(qū)動(dòng)輸人INA 丨 CH2: 驅(qū)動(dòng)輸入INB

CH4:驅(qū)動(dòng)輸出OUT

圖 9. SLM27524 INA滯后INB 2.8ns并聯(lián)波形

CH1: 驅(qū)動(dòng)輸人INA 丨 CH2: 驅(qū)動(dòng)輸入INB

CH4:驅(qū)動(dòng)輸出OUT

04

驅(qū)動(dòng)芯片并聯(lián)應(yīng)用技巧

在驅(qū)動(dòng)芯片并聯(lián)時(shí),外部的一些應(yīng)用條件和應(yīng)用技巧也同樣的重要。

首先,對(duì)于輸入信號(hào)的處理,在PCB上應(yīng)盡量靠近芯片管腳處進(jìn)行并聯(lián)。如果離芯片管腳距離較遠(yuǎn)處并聯(lián)后再分開(kāi)到各個(gè)輸入管腳,那就容易存在PCB走線上的延時(shí)誤差。

其次,輸入通道的門限閾值不完全一致時(shí),會(huì)導(dǎo)致輸出延時(shí)不一樣。為了降低此影響,需增強(qiáng)輸入信號(hào)的上升下降速度。在使用SLM27524時(shí),推薦輸入信號(hào)變化速度不低于50V/us.

圖 10. SLM27524 47V/us上升波形

CH1: 驅(qū)動(dòng)輸人IN 丨 CH2:驅(qū)動(dòng)輸出OUT

圖 11. SLM27524 47V/us下降波形

CH1: 驅(qū)動(dòng)輸人IN 丨 CH2:驅(qū)動(dòng)輸出OUT

最后,為了更好的使芯片在應(yīng)用端使用,推薦在輸出端之間串聯(lián)電阻后再進(jìn)行并聯(lián),按如圖12所示。如果需要OUTA,OUTB進(jìn)行直接并聯(lián),則R1=R2=0。另外可以調(diào)整R1,R2參數(shù),限制直通時(shí)電流值,保護(hù)驅(qū)動(dòng)控制芯片。圖13與圖14顯示了INA,INB之間有17.8ns的延時(shí),如果OUTA,OUTB直接并聯(lián),芯片可能會(huì)燒毀,但OUTA,OUTB之間串接5.1Ω電阻,此時(shí)能夠保證芯片正常工作而不損壞。

圖 12. 芯片輸出端增加輸出電阻

圖 13. SLM27524 INA滯后INB

且OUTA與OUTB串接5.1Ω并聯(lián)波形

CH1: 輸人INA 丨 CH2: 輸入INB

CH3:輸出OUTA 丨 CH4:輸出OUTB

圖 14. SLM27524 INA超前INB

且OUTA與OUTB串接5.1Ω并聯(lián)波形

CH1: 輸人INA 丨 CH2: 輸入INB

CH3:輸出OUTA 丨 CH4:輸出OUTB

05

測(cè)試總結(jié)

綜上所述,在采用驅(qū)動(dòng)芯片并聯(lián)去驅(qū)動(dòng)功率管的應(yīng)用中,除了注意PCB布線布局外,對(duì)芯片對(duì)稱性有較高要求;另外增大輸入信號(hào)變化斜率以及在芯片輸出端串接電阻,可以增強(qiáng)輸出并聯(lián)的可靠性。

審核編輯:劉清

-

PFC

+關(guān)注

關(guān)注

49文章

1062瀏覽量

111235 -

PCB布線

+關(guān)注

關(guān)注

22文章

473瀏覽量

43545 -

校正電路

+關(guān)注

關(guān)注

2文章

32瀏覽量

27705 -

電子電路

+關(guān)注

關(guān)注

78文章

1275瀏覽量

69180 -

驅(qū)動(dòng)芯片

+關(guān)注

關(guān)注

14文章

1644瀏覽量

57959

原文標(biāo)題:應(yīng)用筆記 丨 驅(qū)動(dòng)的并聯(lián)使用

文章出處:【微信號(hào):數(shù)明半導(dǎo)體,微信公眾號(hào):數(shù)明半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

電子電路當(dāng)中 “地” 的介紹

mos管并聯(lián)注意事項(xiàng)

造物數(shù)科亮相華為開(kāi)發(fā)者大會(huì)2025 | 技術(shù)創(chuàng)新與數(shù)字服務(wù),加速電子電路產(chǎn)業(yè)數(shù)智化轉(zhuǎn)型

造物數(shù)科亮相華為開(kāi)發(fā)者大會(huì)2025 技術(shù)創(chuàng)新與數(shù)字服務(wù),加速電子電路產(chǎn)業(yè)數(shù)智化轉(zhuǎn)型

mos管并聯(lián)后共用驅(qū)動(dòng)電阻

工字電感磁芯:電子電路中的關(guān)鍵元件

模擬和數(shù)字電子電路基礎(chǔ)

新概念模擬電子電路(全彩版)

電力電子中的“摩爾定律”(1)

如何抑制電子電路中的噪聲

推薦電子電路從入門到精通

實(shí)用電子電路500例

《新編電子電路大全-合訂本》-1307頁(yè)(全集)

MDD整流二極管的并聯(lián)與串聯(lián)應(yīng)用:如何均流與提高耐壓能力?

在電力電子電路應(yīng)用中為什么需要驅(qū)動(dòng)芯片并聯(lián)使用呢

在電力電子電路應(yīng)用中為什么需要驅(qū)動(dòng)芯片并聯(lián)使用呢

評(píng)論