據說今年的秋招已經開始了,作者君自己之前找工作的時候,記錄下來了一些比較基本的筆試面試題目,分享給大家,希望能幫大家鞏固所學的基本知識。

(因為懶,不想visio畫圖,請大家忍耐一下有些潦草的字跡,謝謝啦)

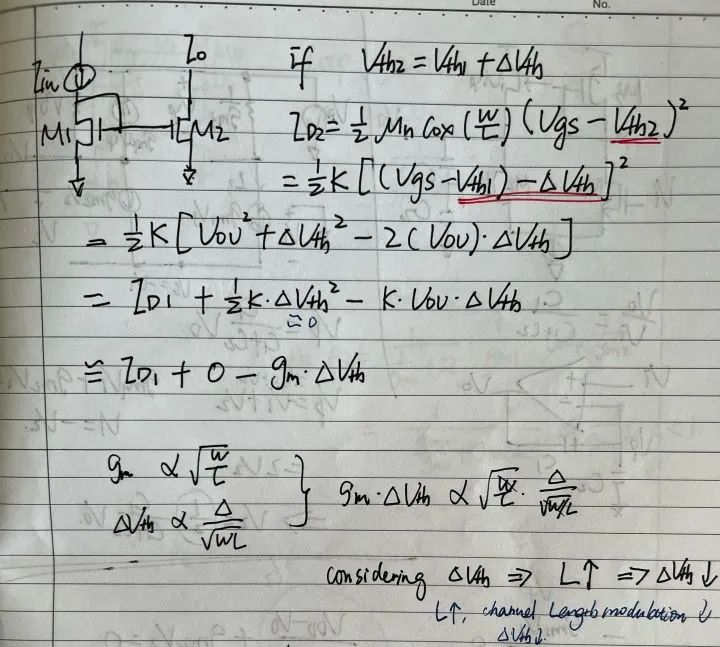

電流鏡的設計考量

這道題主要是考察電流鏡的設計考量。

假如圖中的兩個管子M1和M2之間有mismatch,比如Vth有偏差(偏差是一定有的,特別是當L的取值比較小的時候,越是明顯),如果先忽略掉Vds的影響,需要重視什么變量呢?

按照上面的計算,Id1和Id2之間的差別約等于gm×ΔVth. 又因為gm與寬長比的平方根正相關,而ΔVth的公式里面,長寬的乘積的平方根是在分母位置,分子的Δ是一個跟工藝參數有關的量(我們動不了),所以兩者相乘起來,gm×ΔVth的值和Δ/L正相關。

因此,如果想要減少電流鏡的offset,我們特別需要注意的地方就是兩個管子的L的取值。一般情況下,L取的比較大有利于減小offset。(當然了,電流一定的情況下,L要變大,W自然也要跟著變大,兩者都變大了,有關的寄生電容也會變大……又是一個tradeoff的閉環-_-)

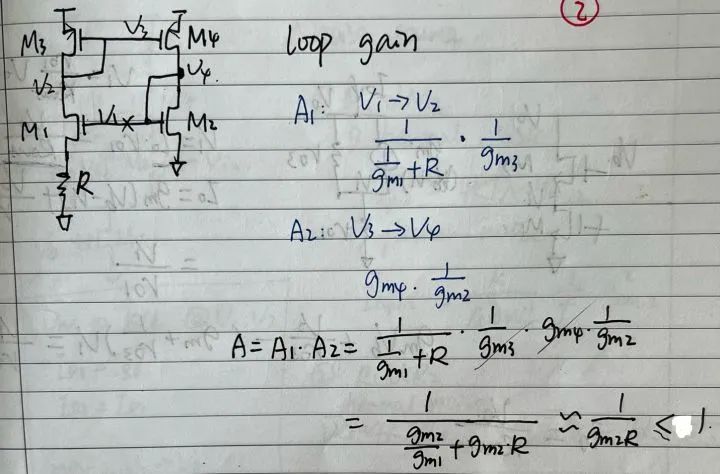

電流產生電路

這道題的考察其實類似bandgap了,問的就是下面那個R到底是應該在M1的下面,還是M2的下面。

如果在M1的gate和M2的gate之間斷開,從V1開始看,經過M1,M3,到M4,M2,可以看出來,這個loop是個正反饋環路。(不知道大家還記不記得我之前提過的很個人的習慣:gate到drain是-,gate到source是+)

對于一個不想讓它震蕩起來的正反饋環路(請回憶一下巴特豪森定律),環路增益必須要小于1.

上面的圖里,我計算了從V1到V2,V2=V3,V3到V4的增益。總的環路增益就是A1乘以A2,約等于1/(gm2R).如果R不是很小,這個A一般來說是小于1的。

PS:如果是典型的constant gm電路,可以讓M1的W是M2的四倍,然后R約等于1/gm2,然后最后生成的電流大致上等于Vov/R. 比較典型的Vov等于兩三百mV,選擇合適的R,就能得到需要的電流。(Razavi的書里figure11.3,如果考慮body effect,Razavi建議把R放在PMOS上面)

大家可以試一下把R放在M2的source下面,可以算出來A大概是gm1?(1/gm2+R).這個乘積一般是大于1的。

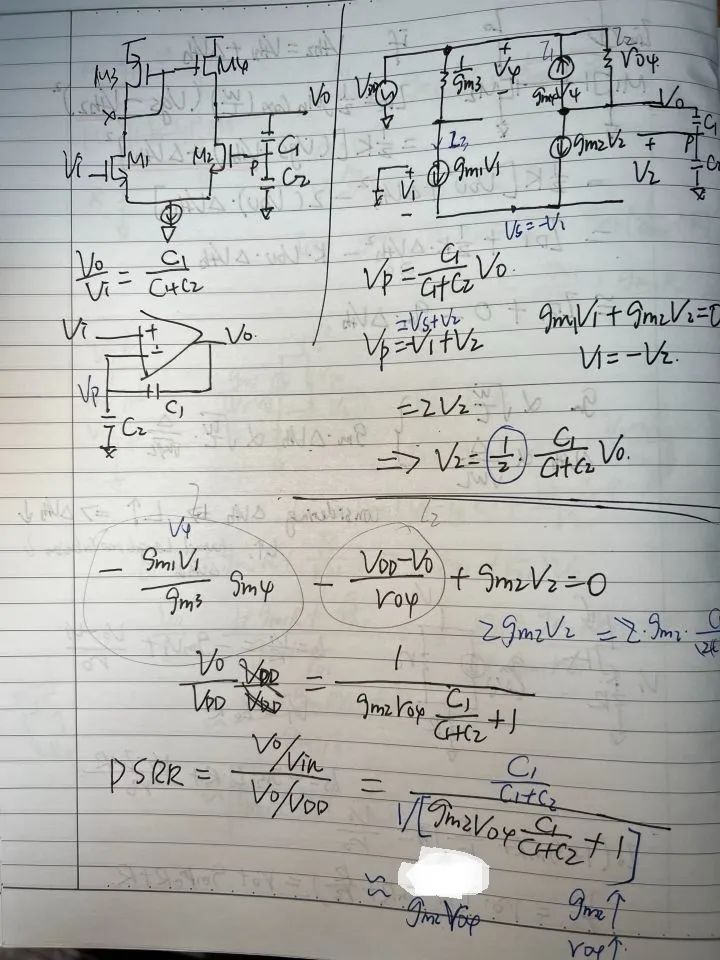

五管運放的PSRR計算

一個掛著C1和C2兩個load的五管運放,計算它的PSRR.

首先畫小信號模型,右上角那一塊。

然后是Vo那里的KCL,得到Vo和VDD之間的關系。已知Vo和Vin的比值是電容分壓,因此可以得到最后的PSRR值是跟gm2ro4的乘積成正比。所以為了增大PSRR,就可以從這兩個變量下手,增大gm2(比如增大寬長比,增大偏置電流),增大ro4(比如M3和M4的L增大),都可以達到目的。

這次的分享就是這三道題。還有一些就留著下次再說吧!讀者們如果也有不錯的題目分享,請留言!謝謝!

審核編輯:湯梓紅

-

運放

+關注

關注

49文章

1229瀏覽量

55621 -

模擬設計

+關注

關注

1文章

57瀏覽量

18818 -

電流鏡

+關注

關注

0文章

44瀏覽量

17783

原文標題:分享一些模擬設計的筆試題目(一)

文章出處:【微信號:analogIC_gossip,微信公眾號:通向模擬集成電路設計師之路】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

TCP三次握手與四次揮手的詳細過程

人工智能工程師高頻面試題匯總:循環神經網絡篇(題目+答案)

用30道電子工程師面試題來拷問墮落的你...

電池模擬設備:充電樁測試負載和電池模擬器的區別?

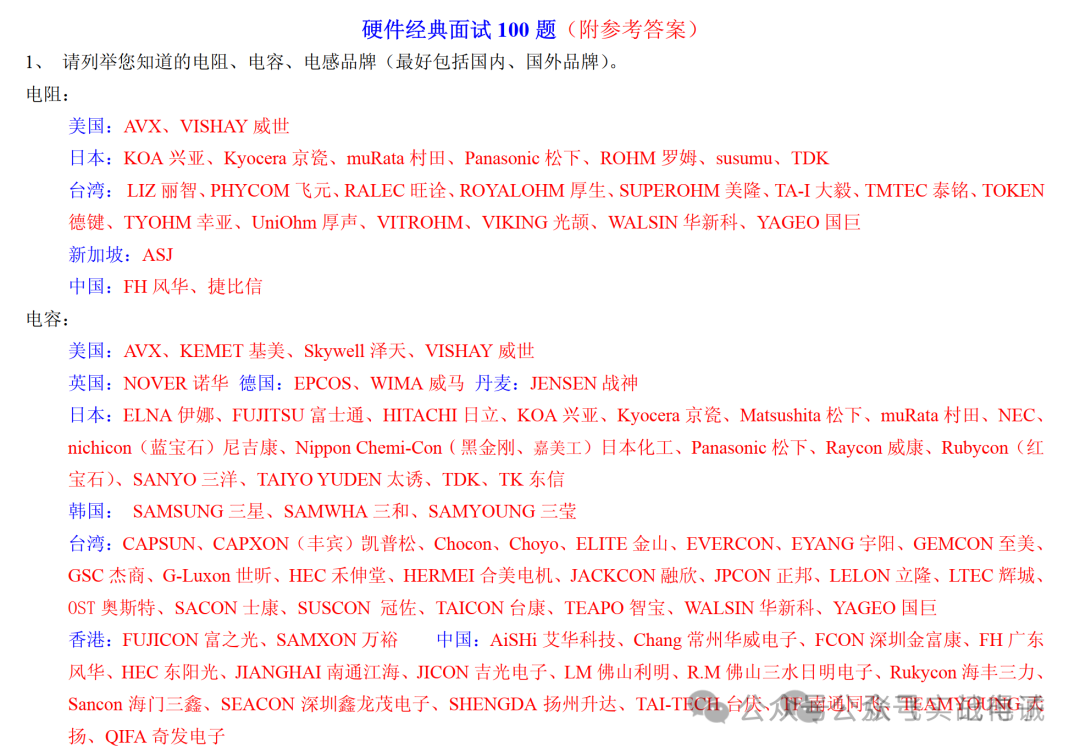

【精選資料】硬件設計指南+無刷電機原理圖大全+工程師面試題庫匯總

每周推薦!硬件設計指南+無刷電機原理圖大全+工程師面試題庫匯總

硬件工程師或研發類筆試面試題庫匯總

常見電子類硬件筆試題整理(含答案)

最全的硬件工程師筆試試題集

常見電子類硬件筆試題整理(含答案)

【硬件方向】名企面試筆試真題:大疆創新校園招聘筆試題

硬件工程師面試/筆試經典 100 題

硬件工程師面試必看試題(經典)

模電與數電的基本知識 (學習備用)

模擬設計的筆試面試題目

模擬設計的筆試面試題目

評論