氮化鎵 (GaN)已成為第三代半導體中事實上的材料。然而,以您需要的質量和您想要的熱阻制造 GaN 晶圓仍然是 Fab 試圖回答的問題。

GaN外延層與硅、藍寶石、碳化硅(SiC)等襯底之間的晶格常數和熱膨脹系數的不匹配導致外延層產生位錯和開裂。

熱管理的常用方法是使用具有高導熱率的基板,例如 SiC 或金剛石作為散熱器。然而,GaN 和 SiC/金剛石之間的晶格失配和熱膨脹系數 (CTE) 失配都使得異質外延非常具有挑戰性。此外,傳統的成核層由于缺陷和結晶度差而表現出低導熱率。由于大部分熱量是在頂部的有源層內產生的,因此具有低導熱率的厚緩沖層會顯著增加從器件到基板的散熱路徑的熱阻。過渡層內、襯底和過渡層之間的界面處的缺陷和邊界散射以及近界面無序共同促成了大的熱阻。

為了生長高質量的 GaN,它需要昂貴的襯底,例如塊體 GaN 和 SiC。因此,器件制造的生產成本明顯高于硅基電子產品。為了實現具有成本效益的最先進的 GaN 功率器件性能,同時有效地管理產生的熱量,可以將外延層從襯底上移除,從而實現襯底的重復使用,并直接結合到散熱器上以提高器件的熱性能. 然而,現有的去除工藝,如涉及光電化學蝕刻、機械剝落和激光界面分解,加工速度慢和/或表面粗糙/開裂明顯,限制了基板重復使用的工藝良率和實用性。因此,這些傳統方法的工藝成本通常超過 GaN 襯底成本,

當設備需要更好的質量時,就缺陷密度、熱性能和汽車、射頻和數據中心應用中的高壓設備所需的更高頻率而言,人們傾向于使用 GaN-on-SiC。

然而,GaN-on-SiC 是一種昂貴的解決方案。一旦在 SiC 襯底上生長出高質量的 GaN Epi 層,您將獲得用于功率和射頻應用的更好的 GaN 器件。缺點是,SiC襯底非常昂貴。GaN Epi 層在其上生長后,不再需要 SiC 襯底。

FSB 的專利技術助您一臂之力

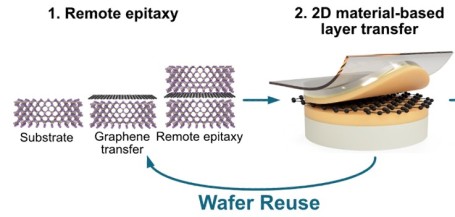

FSB 旨在通過使用獨特的技術以低成本提供高質量和大規模的獨立式 GaN 晶圓和 IP:遠程外延和二維材料層轉移 (2DLT)。

FSB在GaN晶圓技術方面的突出特點如下:

自2017年從麻省理工學院分拆以來,一直以隱形模式孵化

MIT開發的IP全球獨家許可證

FSB擔保的其他專利/知識產權

強大的IP“護城河”保護核心主張

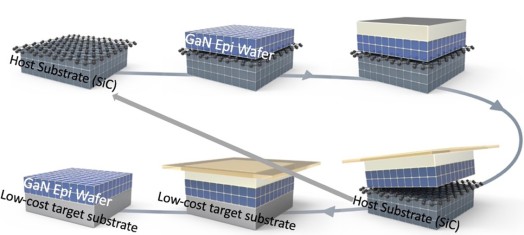

直到現在,還沒有辦法從這種器件結構中去除碳化硅襯底,因此器件變得非常昂貴。FSB,股份有限公司提出了一種由全球專利和專有工藝保護的解決方案,在該解決方案中,您可以創建GaN外延層,并將其從昂貴的SiC襯底上剝離,然后轉移到低成本襯底上。這將釋放碳化硅襯底,以便在下一個氮化鎵外延片生長中重復使用。請參見圖1和圖2。. has come up with a solution secured by global patents and proprietary processes, in which you can create the GaN Epi layer and lift it off from the expensive SiC substrate and transfer it on to a low-cost substrate. This will free up the SiC substrate to be re-used in the next GaN Epi wafer growth. See the Figure 1 and Figure 2.

Figure 1: Wafer Reuse

Figure 1: Wafer Reuse

Figure 2: Processing

Figure 2: Processing

FSB 解決方案的優點是無需任何拋光或其他后處理步驟即可瞬間剝離 GaN 薄膜。粘合或剝離過程不會引入多晶或非晶區。不需要結晶度差的成核層,因此可以獲得超薄(<200 nm)GaN獨立膜。這是任何其他現有技術都無法實現的。

如何驗證技術

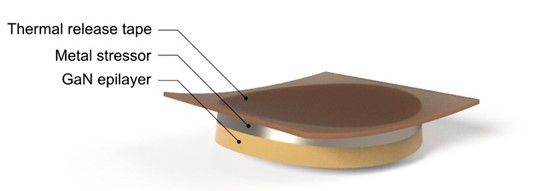

FSB, Inc. 正在對獨立式 GaN 晶圓(圖 3)或轉移到 Si 襯底上的 GaN Epi 層進行采樣。這將使半導體公司能夠制造出具有卓越性能的 GaN 器件。

圖 3:GaN 晶圓

圖 3:GaN 晶圓

FSB, Inc. 現在可以與 Semiconductor Fabs 合作許可和轉讓該技術。或者,FSB, Inc. 可以提供 GaN Epi 晶圓,這些晶圓是發展客戶自己的器件結構和制造 GaN 器件的基礎。FSB 還可以開發客戶特定的器件結構并提供樣品以生產其獨特的 GaN 器件。

審核編輯 黃昊宇

-

半導體

+關注

關注

339文章

30737瀏覽量

264156 -

GaN

+關注

關注

21文章

2366瀏覽量

82350 -

PSB

+關注

關注

0文章

4瀏覽量

7142

發布評論請先 登錄

Neway第三代GaN系列模塊的生產成本

晶圓邊緣曝光(WEE)關鍵技術突破:工藝難點與 ALE 光源解決方案

現代晶圓測試:飛針技術如何降低測試成本與時間

wafer晶圓厚度(THK)翹曲度(Warp)彎曲度(Bow)等數據測量的設備

通過 FSB 的技術解鎖低成本、大規模、優質的 GaN 晶圓

通過 FSB 的技術解鎖低成本、大規模、優質的 GaN 晶圓

評論