【問題1】如何知道ddr3里不空,可以讀取了?

答:DR3和RAM一樣,是一個存儲器件,它的每個內部單元都存儲了當前的數據狀態值。

但DDR3和RAM本身,是沒有“空”、“存有數據”,“數據滿”等概念的。只要給地址,它就會把當前地址的數據給到總線上,而且這個地址可以讀很多次。

在設計的時候,是由設計師用自己寫邏輯來判斷DDR3是否為空。

【問題2】SPI多字節發送是多個字節連在一起發還是分成單字節來進行發送?

答:每款芯片的數據手冊,都會有時序圖的介紹,需要按照芯片數據手冊的要求進行通信。每款芯片的要求都是不同的。所以,您需要查閱數據手冊。

【問題3】如何避免競爭和冒險的情況?

答: 競爭和冒險是由于組合電路中計算的延遲不一致而導致的。它是天然的、不可克服的現象。雖然它不可克服,但在FPGA設計里,它根本就不是一個問題。

因為FPGA都是在D觸發器的時鐘上升沿對電路進行采樣,只要時鐘上升沿前,電路計算結果已經確定,競爭和冒險已經沒有了,那就不會有問題。

那設計時,如何確認時鐘上升沿前,計算結果已經確定了呢?

這就靠時序報告了:時序報告會告訴任何兩個D觸發器之間,它們電路延時之和,從而確認在上升沿之前計算結果確定。

總而言之,設計時不用考慮競爭和冒險;設計完看,看時序報告;沒有問題,那就正常;如果時序報告有問題,就解決時序問題。

【問題4】計數器分頻怎么個不穩定法?

答:1. 時鐘在FPGA里是非常重要的,所有的寄存器都是統一在時鐘的節拍下工作。這個時鐘就相當于一個軍隊的司令部,寄存器都聽從司令部的命令下工作。

2. 一個穩定的系統,時鐘是越少越好。就相當于,一個軍隊,司令部越少越好。如果司令部越多,那么部隊之間的協作必須要增加流程和成本。

3. 計數器分頻的時鐘,無形中增加了時鐘個數,另一方面,就相當于弄一個自己獨立的王國,自然就不穩定。

【問題5】仿真是正確的,但為什么上板就不行?

答:首先要明確,仿真可以而上板不行,這是屬于研發過程中,非常非常之正常的現象,可以說仿真通過后,上板一次性就成功的概率,小之又小。

原因是:仿真只是用電腦模擬運行的情況,它與真實情況可能有所差別。例如:

1. 輸入激勵是您想象出來的,事實上是不是這樣輸入?

2. 您的代碼是否可以綜合出電路?

3. 您的仿真是否測試完所有的情況?

以上都表示了仿真和實際是有差距的,所以不能認為“仿真正確了,上板就正確”。

【問題6】:管腳未分配的現象,老師,我把CPLD的一個引腳接到了LED燈,但是程序中沒有分配這個管腳,第一個版本的程序上電后這個LED燈一直是亮的。

第二個版本上電后LED一直是滅的。這兩個版本的程序,都沒有對這個管腳分配,是什么原因導致的呢?

答:管腳如果未分配,則管腳電平值可認為是不可控,也就是隨機。

【問題7】:FPGA資源不足問題當程序所使用的資源,超出FPGA芯片資源時,如何處理?

答:

1. 按照錯誤提示,判斷是哪種資源不足,如管腳數、RAM、寄存器等。

2. 閱讀資源QUARTUS、ISE和VIVADO的資源報告,查看是哪些模塊占用了哪些資源。

3. 分析該項目程序中各個模塊的資源占用情況,分析代碼,綜合運用多種方法,以求減少資源的使用,如速度換資源;去除冗余的邏輯;降低設計精度;速度換資源等方法。

注意,這些都需要 花費大量時間,一點一點去摳資源。

4. 如果資源依然不足,可以考慮換更高級的芯片;或者改變功能需求等。

【問題8】 就是lvds恢復出數據和時鐘,對齊是需要手動調節時鐘相位,還是寫代碼自動調節?serdes

答:我們做法是手動調節相位對齊。理論上,任何功能都可以使用代碼來調節,只是有沒有必要以及復雜度而已。

【問題9】FPGA生成的DDS數據如何導出到matlab中

答:

1. 可以通過串口、千兆網等接口,傳送到電腦上;

2. 可以采用在線調試工具,如SIGNALTAP、CHIPSCOPE、VIVADO等,捕捉到信號,然后保存的方式得到數據。

【問題10】通常情況下rtl代碼module里面的輸入信號,值是哪里來的呢?

答:

1. 來源于其他模塊的輸出

2. 來源于FPGA外部的管腳,例如按鍵、其他芯片的輸出信號等

【問題11】if(counter<8)請問這句代碼是什么意思呢,按理來說/的優先級高于左移運算符呀?

答:不清楚它要表達的含義。串并轉換的方法,可以參考至簡設設計原理與應用書籍, 串口案例。

FPGA至簡設計原理與應用】書籍連載13 第三篇FPGA至簡設計項目實踐 第四章 串口通信

http://www.fpgabbs.cn/forum.php? ... 13&fromuid=9396

(出處: 明德揚論壇)

【問題12】老師,怎么將信號實現準確的ns級別的延時呢,有什么好思路嗎?[color=rgba(17, 31, 44, 0.56)]

答:正規的做法,就是采用寄存器打拍來延遲,精度為一個時鐘周期

【問題13】lvds和lvds_25有什么區別?

答:主要區別在于內部buffer的供電電源情況,在電氣方面,兩者是等效的(參見數據手冊規格)但是內部的I/O電路配置不同

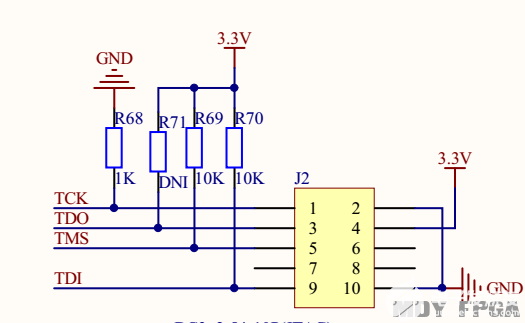

【問題14】xilinx,spartan6的jtag引腳,tck,tms,tdi,tdo需要做上拉處理嗎?

答:這個是ALTERA EP4C的JTAG電路,僅供參考

【問題15】用FPGA輸出0->1或者1->0的信號,我現在想把上升沿或者下降沿的時間拉長到10ms左右,用FPGA的輸出管腳可以實現嗎?

答:FPGA直接輸出的數字信號,上升沿和下降沿都是很快就完成變化的。如果要控制變慢,其實就是輸出固定電平的信號,那么這個需要外置DAC來實現。

【問題16】我們的TFT顯示屏是工作在DE模式,是吧?

答:我們的案例默認使用的是DE模式,如果需要非DE模式,可以手動修改底板硬件實現。

【問題17】很多的數字電子元件的引腳都是要求有明確的電平(0/1),但是有個別的器件引腳鏈接時,可以處于懸空狀態

【但很多的教材上寫的 引腳不能懸空,因為可能導致數字邏輯電路的狀態不確定】,這一點如何理解呢~?

答:對于這種引腳,需要去看對應芯片的數據手冊,一般里面都會有介紹說明的。

【問題18】CPLD是沒有IP核可以使用嗎?

答:看要使用的ip核是什么類型,像RAM、FIFO等固有資源都是有IP核的

【問題19】實質的時鐘周期與仿真時鐘周期有差別,這個差別會累積起來嗎?

答:仿真的時候使用的是理想時鐘,例如50M時鐘,在實質的板上不可能完全等于50M的,一定有差別。

這種差別的積累,可能會對“總時間”有影響,例如計算1秒時鐘,那么就有可能有差別了。

但這種差別的積累,不會產生時序的混亂:因為FPGA內,所有D觸發器,都是在一個時鐘周期內計算完的,只要滿足時序要求,不關心實際頻率是多少,總之上升沿來就計算一次。

如不清楚,請仿真,嘗試用不同周期的時鐘來對同一個電路仿真。

【問題20】如果扇出很大,high fanout 到了4000多,要怎么優化?

答: 扇出是指一個信號驅動了很多其他信號(即這個信號是其他很多信號的產生條件),FPGA對扇出數量有要求,不能扇出太多。

如果扇出太多了,該怎么優化呢?現舉例如下:

假設信號A,驅動了信號BCDEFG,即扇出數為6。優化思路是:讓A用寄存器分別產生信號A1和A2,再用A1驅動信號BCD,用A2驅動信號EFG。這樣扇出數減少為3。

【問題21】如果FPGA芯片沒有時鐘晶振,其他IO口是不是就不能輸入數據呀。晶振影響輸入數據不?

答:要看輸入是否需要時鐘。

例如:使用串口的時候,在電路上就接收和發送兩根線,沒有用到時鐘,所以晶振不影響。而攝像頭輸出圖像的時候,需要先給攝像頭一個時鐘,再進行相關的配置,這時晶振就有影響。

【問題22】異步信號慢時鐘域采集到快時鐘域的方法有嗎?

答:1、使用FIFO進行跨時鐘域處理

2、慢時鐘域的信號到快時鐘域,是可以被采集到的,跨時鐘域之后進行打拍,使其同步化即可

【問題23】工程中經常使用的sop表示第一個有效數據、eop表示最后一個有效數據、mty表示無效字節數等,這些都是那些單詞的縮寫?

答:習慣性引用了華為項目時的縮寫,具體不清楚。

溫馨提示:明德揚除了培訓學習還有元器件一站式配單業務,人工服務的模式采購,采購**人員聯系方式:明德揚元器件一站式配單服務咨詢:易老師13112063618(微信同號)

審核編輯:湯梓紅

-

FPGA

+關注

關注

1660文章

22416瀏覽量

636602 -

matlab

+關注

關注

189文章

3025瀏覽量

238764 -

DDR3

+關注

關注

2文章

288瀏覽量

44156 -

計數器

+關注

關注

32文章

2316瀏覽量

98218 -

DDS

+關注

關注

22文章

684瀏覽量

156619

發布評論請先 登錄

儲能EMS控制器(5) — 儲能柜調試又慢又不穩定怎么辦?

系統從DeepSleep下喚醒時鐘默認為原時鐘,如果原時鐘頻率特別高,是否有存在啟動不穩定問題?

頻率計數器/定時器 時間間隔計數器的應用領域和范圍的深度解析 頻率計數器模塊

船舶供電不穩定?華興CXK控制變壓器來救場?

JGN8-M18-OP接近開關信號不穩定怎么辦

工廠電壓不穩定,選 380V 交流穩壓器看這里!

雷電(雷擊)計數器的原理、作用及行業應用解決方案

安裝了EZ-USB?套件1.3.4自1.3.5版固件運行不穩定如何修復?

基于 FPGA 的任意波形發生器+低通濾波器系統設計

ADXRS645的175℃高溫陀螺儀傳感器,測試不穩定怎么解決?

吸塵器啟動不穩定?硬件、算法、系統集成三大策略,穩定啟停20000次--其利天下

使用FPGA對LTM4678進行配置,只要配置電壓大于2.75V,就會出現輸出電壓不穩定的情況,怎么j

信號傳輸不穩定?德索BNC型射頻連接頭來拯救

計數器分頻怎么個不穩定法 FPGA生成的DDS數據如何導出到matlab中

計數器分頻怎么個不穩定法 FPGA生成的DDS數據如何導出到matlab中

評論