可以肯定地說,現在的計算世界如此豐富多彩,PCIe標準的貢獻功不可沒。

在處理器面世的頭些年,整個計算領域的各個方面都在高速發展。但進入到上世紀80年代后,隨著處理器的速度越來越快。以至于當時流行的總線帶寬已經滿足不了CPU的需求,并逐漸成為制約計算機處理能力進一步提高的瓶頸。于是在1991年,Intel、IBM、HP、Compaq、DEC等100多家計算機公司成立了PCISIG,聯合推出PCI(Peripheral Component Interconnect),并于次年發布了PCI1.0標準。

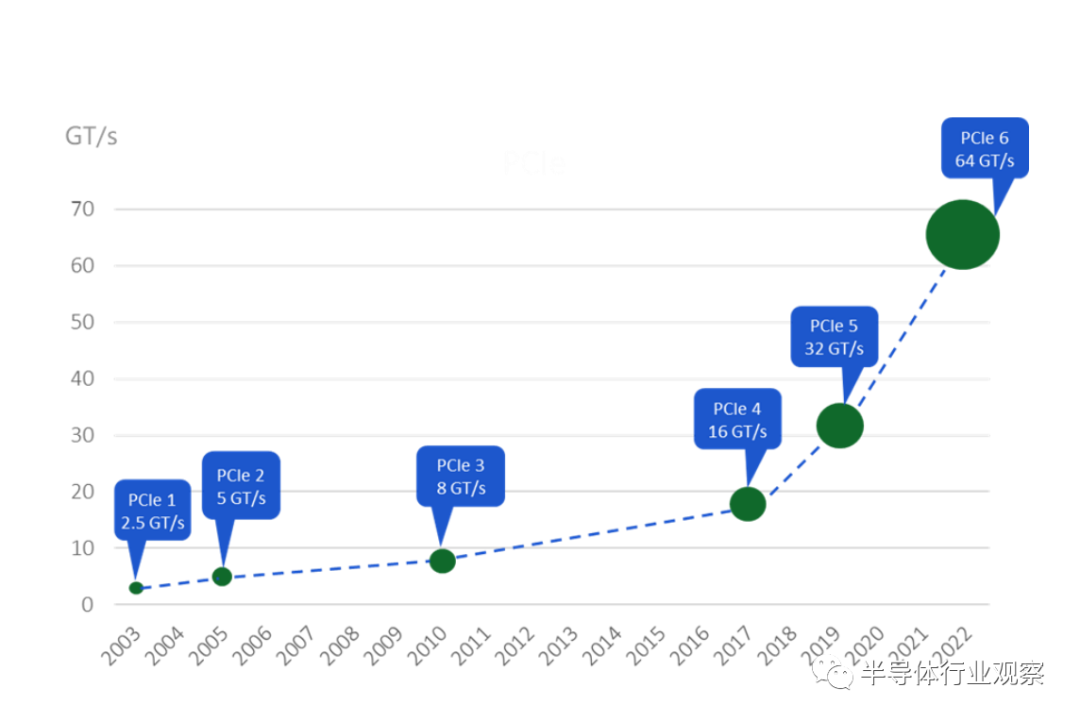

但在后續的發展中,行業參與者發現PCI還是不能滿足總線的需求,于是他們又在接下來的日子里繼續對其進行更新升級,并于2003年推出了廣為人知的PCIe標準。和在PCI總線上同時掛接多個I/O設備不同,PCIe標準采用了點對點串行連接,物理上只能連接一個設備。通過在物理層、鏈路層和傳輸層的定義和升級,PCIe逐漸成為數據中心和計算應用中芯片間數據傳輸的行業標準。隨著終端的需求,也在今年1月正式進入了PCIe 6.0時代。

如上圖所示,每一代的PCIe標準較之上一代,都實現了較大的速度提升。為了達成這個目的,PCIe 6.0做了一些不同以往的新升級。

PCIe 6.0改變了什么?

對于全新標準,首先從速度上看,和以往的標準一樣,PCIe 6.0同樣實現了翻倍提升——獲得了高達64GT/s的速率體驗。同時,新標準還克服了整個通道傳輸長度以及距離的限制,具備前向糾錯(FEC)以及固定大小數據包(Flit)等新特性。其中,在速度方面的提升,則主要是通過采用新的PAM4調制信號方式實現。

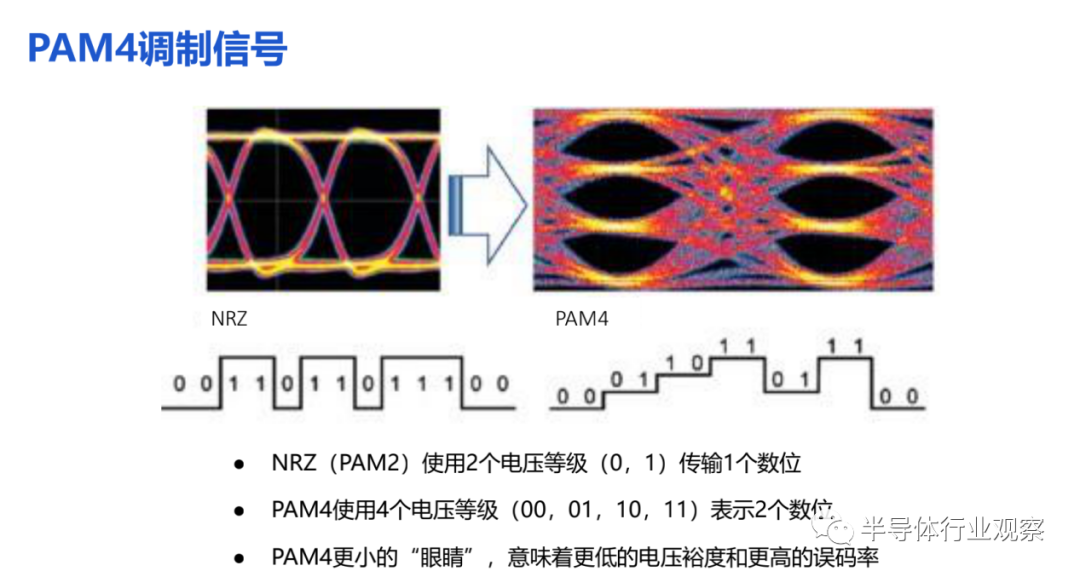

從Rambus 戰略營銷副總裁Matt Jones的介紹我們得知,在PCIe 6.0以前,PCIe一直采用的是NRZ調制信號方式,也就是“ Non-Return-to-Zero ”——不歸零編碼。在實際應用中,這種編碼模式采用0或1兩個電壓等級,每一個時鐘周期只能傳輸1bit的信號。也就是說它只采用了高低兩種信號電平。因此,與采用四電平的PAM4相比,我們也將NRZ稱作PAM2 。

在以前的標準,這種編碼模式還是能夠實現其規定的速度,但進入到PCIe 6.0,PAM 4的采用是刻不容緩了,這主要與奈奎斯特頻率有關。根據維基百科,奈奎斯特頻率(英語:Nyquist frequency)是離散信號系統采樣頻率的一半,因瑞典裔美國工程師哈里·奈奎斯特(Harry Nyquist)或奈奎斯特-香農采樣定理得名。采樣定理指出,只要離散系統的奈奎斯特頻率高于被采樣信號的最高頻率或帶寬,就可以避免混疊現象。

回到PCIe標準上,據介紹,在進入PCIe 5.0時代后,數據速率的增加,也讓奈奎斯特頻率從8GHz加倍到16GHz,這就使得PCIe 5.0的頻率相關損耗比PCIe 4.0要嚴重得多。再加上電容耦合(噪聲和串擾)的增加,使得PCIe 5.0通道成為最難處理的NRZ通道。換而言之,如果PCIe 6.0仍然保留NRZ信號,則奈奎斯特頻率將增加到32GHz,通道損耗大于60dB,這對于實際系統而言太大了。這就是我們需要從NRZ更改為PAM-4的原因。這一變化意味著發射和接收的信號現在有四個不同的電壓電平,而不是兩個。

PAM4是PAM(Pulse Amplitude Modulation,脈沖幅度調制)調制技術的一種。作為NRZ(NonReturn-to-Zero)后的熱門信號傳輸技術,PAM4是多階調制技術的代表,當前也被廣泛應用在高速信號互連領域。 Matt Jones也指出,通過PAM4,每個時鐘周期的數據傳輸可以達到2bit,而并不僅僅是單bit的數據傳輸。又因為PAM4采用四個不同的電平等級,因此能在每個時鐘周期表達2個數位,分別是00、01、10再到11。這就意味著在同樣的電壓波動范圍之內和同樣的時鐘周期內,由于PAM4的電壓等級比PAM2高了兩個,即眼圖中黑色的區域“眼睛“這個部分更多、更小了。

“這種變化帶來了另外兩個重要的影響,即更低的電壓裕度和更高的誤碼率,使得在設備中保證信號完整性成為了一個非常關鍵的難題。”Matt Jones強調。

至于前文談到的前向糾錯技術(FEC),按照Matt Jones所說,這是為了在保持數據傳輸速率的前提下解決PAM4本身的問題。而這種算法技術則恰好可以在數據傳輸鏈路中確保所有信號的完整性。

“同時,FEC技術的采納還改變了數據流控制單元的情況,要求我們也必須針對數據包本身的大小做出調整和改變。在PCIe 6.0之前的幾代規范采用的都是可變大小的數據包。但由于FEC技術的采納,PCIe 6.0必須采用固定大小數據包(FLIT),以更好地保證FEC技術的實現和操作。”Matt Jones接著說。

為了減少整體系統的能耗,PCIe 6.0還采用了顛覆式的L0p模式,其本質是通過動態的信道分配,允許將每個通道進行封閉或者打開來實現系統性的節能。

PCIe 6.0的關鍵

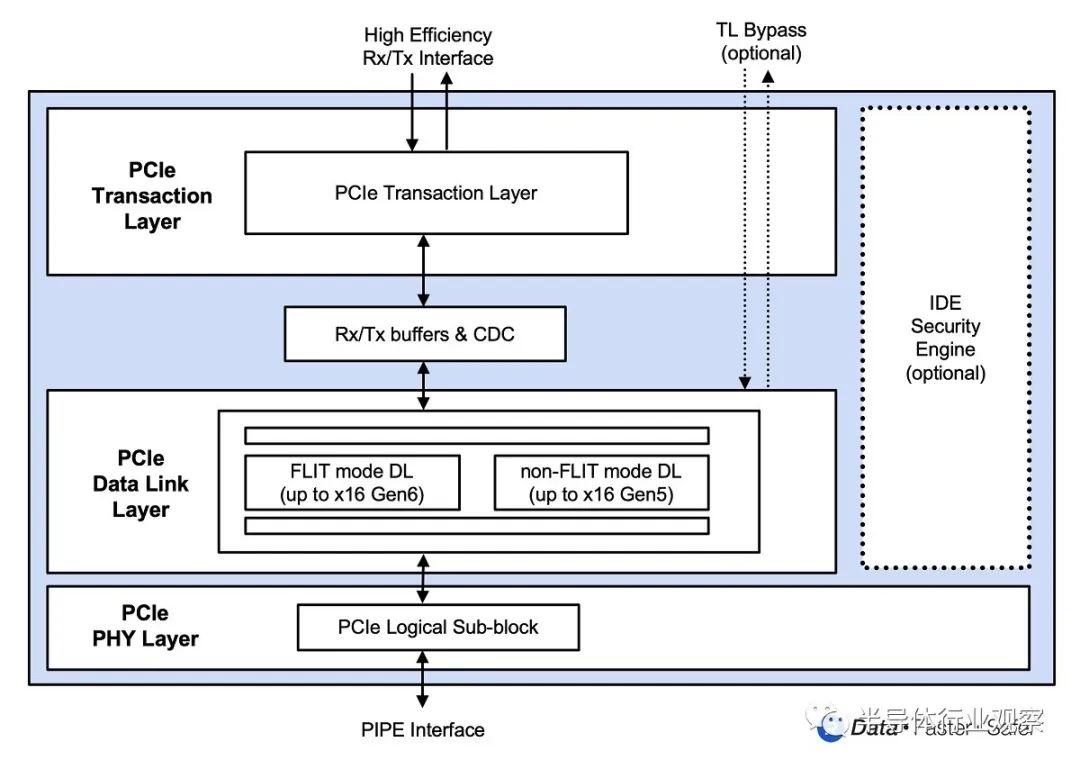

熟悉PCIe的讀者應該知道,所有的PCIe外設要想連接到系統上,關鍵就在于其控制器。因為多個標準的出現,市場對PCIe 控制器又提出了更多的需求。以PCIe 6.0 控制器為例,不但要要支持 PHY Interface for PCI Express (PIPE) 規范的 6.x 版,還要向后兼容 PCIe 5.0、4.0 和 3.1/3.0 規范。并且能夠滿足眾多客戶和行業用例,例如可配置為支持端點、根端口、交換機端口和雙模拓撲,以幫助實現多種使用模型。

因為終端對速度的需求量猛增,市場對PCIe 6.0也翹首以待,作為這個市場的重要玩家之一,Rambus也推出他們全新的PCIe 6.0 控制器。

Matt Jones告訴記者,Rambus的PCIe 6.0控制器不但數據傳輸速率能達到新標準設定64GT/s。更重要的一點是,該控制器還集成了完整性和數據加密(IDE)引擎,使其可以實現數據在不同PCIe設備的PCIe通路之間的安全傳輸。同時,該控制器在功耗、面積以及延遲上都特別進行了相應的優化,特別在降低能耗方面,以幫助確保PCIe 6.0成為數據中心解決方案的一塊關鍵基石,進而推動環保型數據中心的建設,并減少對散熱管理的需求,降低擁有成本。

此外,Rambus的PCIe 6.0控制器還非常靈活,可以適用于PCIe端點、根端口、雙模式和交換機端口配置。

Rambus總結道,公司PCIe 6.0控制器的主要特性包括但不限于:支持PCIe 6.0規范,包括64 GT/s數據傳輸速率和PAM4信令;支持實現高帶寬效率的固定大小的FLIT;實現低延遲前向糾錯 (FEC) 以提高鏈路穩健性;內部數據路徑大小可根據最大值自動放大或縮小(256、512、1024 位)鏈接速度和寬度,以減少門數和優化吞吐量;向后兼容PCIe 5.0、4.0和3.0/3.1;支持端點、根端口,以及雙模式和交換機端口配置以及針對性能進行了優化的集成IDE。

Matt Jones指出,PCIe 6.0早期的使用場景是高性能計算的應用(如AI加速器),這些計算密集型應用通常選擇的節點是高級節點,尤其集中在5納米和3納米。但是,隨著PCIe 6.0在未來的成熟,進入到其他的應用領域,可能更多使用者會考慮成本因素,并轉向不那么先進的節點。

Matt Jones同時強調,Rambus的PCIe 6.0的控制器將成為ASIC供應商的重要基石,幫助他們為AI/ML加速器建立起一個更加完善的PCI生態系統,并支持不斷發展的數據中心中PCIe 6.0級數據傳輸的基礎設施。

除了PCIe以外,Rambus還在備受關注的CXL(Compute Express Link)標準上扮演先鋒者的角色。這是一種開放式互連新標準,面向 CPU 和專用加速器的密集型工作負載,這些負載都需要在主機和設備之間實現高效穩定的存儲器訪問。

Rambus 大中華區總經理蘇雷透露,在去年,Rambus發布CXL內存互連計劃,推出了一系列面向數據中心的新的解決方案,目標是讓數據中心架構進入下一個更高效節能的新階段。他進一步指出,現在已經有廠商在CXL的合作上與Rambus進行了溝通。展望未來,CXL也會推出池化的概念,這將幫助下一代的數據中心變得更加高效化、節能化,以一種新的架構來迎合數據中心的未來需求。

之所以Rambus能夠在總線技術上擁有那么如此實力,如蘇雷所說,這從公司的名稱上可以體現的淋漓盡致。他表示,Rambus可以拆分為RAM和BUS,其中RAM代表內存,BUS是總線,這也代表了公司的兩個發力方向。在歷經多年的發展,Rambus也已經積累了3000多項專利和應用,公司的主要業務也涵蓋了基礎專利授權、芯片IP(接口IP和安全IP)授權以及內存接口芯片。

正因為擁有如此豐富的技術根基,這讓他們能夠為全球客戶提供全方位服務。具體到中國方面,蘇雷表示,Rambus會緊密聯系中國產業鏈上下游伙伴,除了提供優異性能的產品外,還提供緊密高效的技術支持。“我們將自身的技術經驗分享給客戶,以在設計階段就給客戶一些建議和指導,幫助客戶的產品以高質量更快上市。這也深得客戶的支持和歡迎,并且讓他們的產品更有競爭力。”蘇雷最后說。

審核編輯 :李倩

-

cpu

+關注

關注

68文章

11279瀏覽量

224991 -

PCIe

+關注

關注

16文章

1461瀏覽量

88422

原文標題:關于PCIe 6.0,你需要知道的!

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

JH7110 中的 PCIE 器件有什么用途?

PCB設計時需要知道的16個概念分享

什么是ARM架構?你需要知道的一切

PCIe 6.0 SSD主控芯片狂飆!PCIe 7.0規范到來!

曙光存儲超級隧道技術助力應對PCIe 6.0時代

已收藏!你需要知道的57個常用樹莓派命令!

關于 樹莓派5 超頻:你需要知道的一切!

攜手Synopsys與Keysight C位出道 | Samtec PCIe 6.0 Demo

Diodes公司PCIe 6.0時鐘緩沖器介紹

關于PCIe 6.0,你需要知道的!

關于PCIe 6.0,你需要知道的!

評論