安全問(wèn)題通常集中在處理器上執(zhí)行的軟件上。但是,并非所有電子功能都可以在軟件中運(yùn)行。FPGA提供了另一種工作方式,并且比軟件中執(zhí)行的功能更安全。

FPGA提供了更多的硬件控制,并且對(duì)于攻擊者而言更加不透明。對(duì)于嵌入式FPGA,設(shè)計(jì)人員可以完全控制整個(gè)系統(tǒng)。這意味著更少依賴其他人設(shè)計(jì)的硬件。這也意味著最終設(shè)計(jì)不可能公開(kāi)記錄,這意味著在進(jìn)行許多攻擊之前必須進(jìn)行艱巨的逆向工程任務(wù)。

Flex Logix首席執(zhí)行官Geoff Tate表示:“如果您擔(dān)心安全性,那么在某些情況下,要有人破解,F(xiàn)PGA塊將變得更加困難。

通過(guò)編寫在處理器上執(zhí)行的軟件,可以實(shí)現(xiàn)大量的電子功能。已經(jīng)充分記錄了安全隱患和保護(hù)此類系統(tǒng)的需求。但是,F(xiàn)PGA還是一種在硬件而非軟件中實(shí)現(xiàn)功能的流行方法。盡管有時(shí)這是ASIC專用硅電路的前奏,但FPGA加速器在數(shù)據(jù)中心中很流行。需求可能迅速變化的新興行業(yè)中的設(shè)計(jì)也可以使用FPGA。

基于FPGA的系統(tǒng)中的安全性不亞于基于處理器的系統(tǒng)中的安全性。但是,F(xiàn)PGA有一些根本的區(qū)別,可以幫助完成安全任務(wù)。主要區(qū)別與信息可用性和硬件工程師所具有的控制有關(guān)。

更難破解您不知道的東西

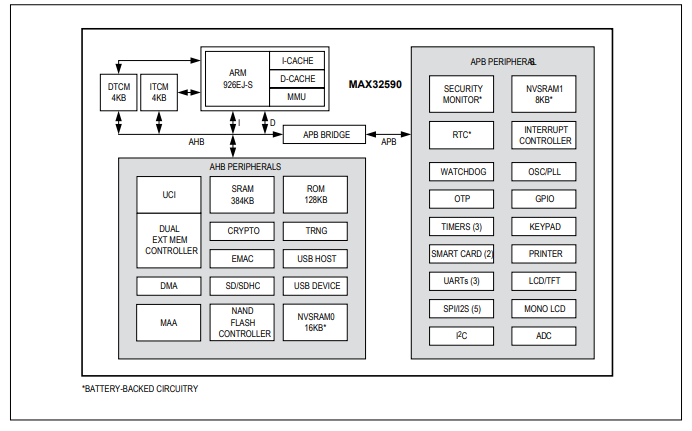

處理器是由硬件公司制造的,還是由IP公司設(shè)計(jì)的以包含在SoC中。在后一種情況下,將處理器集成到芯片中的硬件團(tuán)隊(duì)對(duì)處理器模塊的可見(jiàn)性有限。重點(diǎn)在于互連,而不是處理器中邏輯的細(xì)節(jié)。配置和連接后,該處理器可供軟件工程師用于創(chuàng)建代碼。

為了創(chuàng)建代碼,必須很好地記錄處理器的硬件體系結(jié)構(gòu)。指令集,流水線,I / O,存儲(chǔ)器架構(gòu),內(nèi)部時(shí)序-所有這些都必須已知,以便創(chuàng)建性能最佳的軟件。但是,所有這些信息的可用性也使處理器處于危險(xiǎn)之中,因?yàn)樗粌H對(duì)善意的編碼人員可用,對(duì)于尋求弱點(diǎn)和入侵方式的攻擊者也可用。

FPGA不那么透明。現(xiàn)成的版本具有詳細(xì)記錄的高級(jí)體系結(jié)構(gòu),但較低級(jí)的細(xì)節(jié)留給了設(shè)計(jì)軟件。盡管處理器必須容納想要使用匯編語(yǔ)言工作并管理每個(gè)時(shí)鐘周期的程序員,但很久以前,F(xiàn)PGA設(shè)計(jì)就失去了手動(dòng)控制不同邏輯模塊配置方式的能力。設(shè)計(jì)的規(guī)模是如此之大,以至于實(shí)際上,布局布線工具在完成整個(gè)設(shè)計(jì)方面的工作要比手動(dòng)調(diào)整要好得多。

結(jié)果,F(xiàn)PGA沒(méi)有記錄手動(dòng)設(shè)計(jì)所需的底層細(xì)節(jié)。甚至用于配置FPGA的位流也沒(méi)有記載。可以對(duì)其中的一些細(xì)節(jié)進(jìn)行逆向工程,但這需要大量工作-比了解處理器所需的工作要多得多。泰特觀察說(shuō):“祝你好運(yùn),找出[比特流]中的哪些比特流向何處。” 嵌入在SoC(eFPGA)中的FPGA架構(gòu)甚至更加晦澀難懂。“當(dāng)您談?wù)撉度胧紽PGA時(shí),難度更大。”

此外,處理器傾向于控制整個(gè)系統(tǒng),同時(shí)還托管需要運(yùn)行的各種軟件程序。因此,即使FPGA可以控制系統(tǒng),這也不是典型的。通常由處理器負(fù)責(zé),F(xiàn)PGA加速特定的委托任務(wù)。對(duì)處理器的攻擊有使攻擊者控制系統(tǒng)的風(fēng)險(xiǎn),但這對(duì)于FPGA攻擊來(lái)說(shuō)是不太可能的結(jié)果。Tate說(shuō):“即使您控制了FPGA,也無(wú)法控制系統(tǒng)。”

在管理通信時(shí),處理器也占據(jù)著中心位置,因此通信通道成為嘗試訪問(wèn)處理器的一種方式。FPGA傾向于在較低的體系結(jié)構(gòu)級(jí)別上運(yùn)行,因此通過(guò)通信通道進(jìn)行攻擊可能不太成功。

文檔可能不是基于處理器的系統(tǒng)的唯一漏洞。使用處理器可以更輕松地探查發(fā)現(xiàn)正在發(fā)生的事情甚至影響行為的能力。Mentor FPGA解決方案經(jīng)理Ray Salemi說(shuō):“ FPGA比基于處理器的系統(tǒng)提供更好的安全性,因?yàn)榛谔幚砥鞯南到y(tǒng)容易遭受反復(fù)試驗(yàn)的攻擊,在這種情況下,對(duì)手使用諸如內(nèi)存緩沖區(qū)溢出之類的技術(shù)來(lái)改變處理器的行為。西門子業(yè)務(wù)。“另一方面,F(xiàn)PGA在啟動(dòng)時(shí)從ROM加載其配置位,并且數(shù)據(jù)無(wú)法通過(guò)數(shù)據(jù)路徑修改底層邏輯。”

如果您處于控制之中,則更容易確保安全。處理器,無(wú)論是預(yù)先設(shè)計(jì)的還是可配置的IP,都只能為硬件設(shè)計(jì)人員提供有限的控制權(quán)。現(xiàn)成的處理器無(wú)法控制。就是這樣。SoC中的處理器IP提供了更高級(jí)別的控制,但仍處于較高級(jí)別,您可以在其中指定諸如可以放置多少個(gè)不同塊的實(shí)例或可以創(chuàng)建多少個(gè)I / O的東西。Tortuga Logic的聯(lián)合創(chuàng)始人兼首席技術(shù)官Jason Oberg表示:“有了SoC,實(shí)際硬件的內(nèi)部就是一個(gè)黑匣子。” “您可以在軟件級(jí)別配置什么東西,但是您真的不知道軟件如何與硬件交互。”

這些模塊和I / O的詳細(xì)設(shè)計(jì)不受芯片設(shè)計(jì)人員的控制。當(dāng)然,這是有意的-這是IP提供的提高生產(chǎn)力的基礎(chǔ)。但是,該IP的購(gòu)買者無(wú)法糾正任何安全漏洞。Oberg說(shuō):“您控制和分析的系統(tǒng)越多,對(duì)系統(tǒng)的了解,對(duì)安全性的了解以及整體保證就越高。”

借助現(xiàn)成的FPGA,硬件設(shè)計(jì)人員可以完全控制在FPGA架構(gòu)中實(shí)現(xiàn)的邏輯。OneSpin Solutions信任與安全產(chǎn)品經(jīng)理John Hallman表示:“之所以認(rèn)為FPGA安全性更高,是因?yàn)槟梢詫?duì)設(shè)計(jì)進(jìn)行定制而不是別人定制。” “最后一件定制作品是您的。”

驗(yàn)證也更加透明。Oberg說(shuō):“在構(gòu)建自己的定制ASIC的FPGA中,您將進(jìn)行更多的白盒分析。” “這使您可以研究許多不同的極端情況,并幫助您設(shè)計(jì)出更強(qiáng)大的系統(tǒng),而不必相信供應(yīng)商已正確地做到了這一點(diǎn)。”

但是,F(xiàn)PGA中還有很多其他邏輯,設(shè)計(jì)人員無(wú)法控制。至少,有支持FPGA配置的硬件基礎(chǔ)架構(gòu)。許多FPGA還具有強(qiáng)化的處理器和其他模塊。Oberg指出:“在現(xiàn)代的基于SoC的FPGA中,您仍然非常依賴FPGA的ASIC部分來(lái)安全地構(gòu)建該部分。” 使用這種FPGA的硬件設(shè)計(jì)人員幾乎無(wú)法控制這些硬邏輯模塊。

嵌入式FPGA(eFPGA)提供了更多控制。將FPGA模塊連接至系統(tǒng)其余部分的所有邏輯均在設(shè)計(jì)人員的控制之下。Oberg說(shuō):“對(duì)于eFPGA,您正在構(gòu)建自己的ASIC,并且可以完全控制整個(gè)過(guò)程-實(shí)際比特流的加載方式和存儲(chǔ)位置。” 連接到FPGA的所有模塊均由設(shè)計(jì)團(tuán)隊(duì)選擇或設(shè)計(jì)。關(guān)于安全漏洞的任何擔(dān)憂都可以通過(guò)現(xiàn)成的FPGA來(lái)解決。

當(dāng)然,這是一把雙刃劍。Hallman告誡說(shuō):“嵌入式FPGA為您提供了可重編程邏輯的領(lǐng)域,但沒(méi)有為您提供保護(hù)該邏輯的模板。” “由集成商來(lái)定制您的安全性取決于您。您必須提出安全計(jì)劃和驗(yàn)證計(jì)劃,以確保所部署的內(nèi)容滿足您的安全需求。” 因此,只有在設(shè)計(jì)者知道如何實(shí)現(xiàn)所有必要的安全細(xì)節(jié)時(shí),收益才會(huì)累積。

構(gòu)建包含處理器,片上存儲(chǔ)器和eFPGA的SoC還有一個(gè)安全優(yōu)勢(shì)。這意味著更多的信號(hào)保留在芯片上,使它們更難監(jiān)聽(tīng)。Synopsys的高級(jí)市場(chǎng)經(jīng)理Joe Mallett說(shuō):“使軟件和硬件在同一設(shè)備上協(xié)同工作具有潛在的好處。” “外部存儲(chǔ)器交互作用有限,通道更加安全,軟件和硬件之間的緊密耦合。”

像軟件一樣,F(xiàn)PGA代碼也可以更新,以改善功能并修復(fù)安全漏洞。Hallman說(shuō):“人們正在FPGA中進(jìn)行無(wú)線‘固件’更新,您可以在其中修改基礎(chǔ)硬件功能。” 但是更新FPGA比更新軟件更為嚴(yán)格。“傳統(tǒng)上,更新FPGA被視為一個(gè)更強(qiáng)大的過(guò)程。”

改變FPGA代碼的方式要能提供新的所需功能,同時(shí)又能適應(yīng)舊的界限,達(dá)到正確的時(shí)序,并且堅(jiān)持現(xiàn)有的I / O比改變軟件更困難。但是它仍然有價(jià)值。Hallman說(shuō):“肯定存在無(wú)法在特定區(qū)域關(guān)閉計(jì)時(shí)的風(fēng)險(xiǎn)。” 這些挑戰(zhàn)仍然存在,但是與ASIC相比,您至少有重新配置的機(jī)會(huì)。好了一步。”

也就是說(shuō),安全軟件堆棧將依賴于內(nèi)置在硬件中的安全功能。如果該硬件已更新,則可能會(huì)破壞軟件堆棧。“可以對(duì)安全硬件進(jìn)行更新以滿足當(dāng)前的需求,但是與此同時(shí),它可能會(huì)使舊的軟件堆棧停止工作,” Mallett指出。“由于同時(shí)對(duì)硬件和軟件進(jìn)行了強(qiáng)制更新,因此這可能是一個(gè)好處。”

但是,在處理器的控制下重新配置eFPGA會(huì)帶來(lái)另一個(gè)漏洞。Salemi說(shuō):“嵌入式eFPGA顯示安全性僅與最弱的鏈接一樣強(qiáng)。” “如果可以通過(guò)SoC中的嵌入式處理器來(lái)重新配置eFPGA,則控制了嵌入式CPU的對(duì)手可以重新配置嵌入式FPGA以安裝后門。例如,人們可以重新配置eFPGA來(lái)實(shí)現(xiàn)以前受損的通信接口版本,從而開(kāi)放整個(gè)芯片進(jìn)行攻擊。”

這些擔(dān)憂在安全性和安全性重疊的汽車,機(jī)器人技術(shù)和航空電子等市場(chǎng)引起了熱議。除了典型的安全措施外,還需要監(jiān)視片上數(shù)據(jù)流量模式,以識(shí)別違規(guī)行為的異常行為。對(duì)于熱點(diǎn)或異常熱活動(dòng)也是如此,這可能與正常老化和使用情況相關(guān)或無(wú)關(guān)。

Xilinx芯片營(yíng)銷總監(jiān)Manuel Uhm表示:“我們?cè)鰪?qiáng)了安全性功能,可防止發(fā)生差分功率攻擊等事件。“在模具中,我們還具有多個(gè)溫度傳感器,因?yàn)槟梢垣@得熱點(diǎn),而客戶需要知道這些熱點(diǎn)在哪里,以適應(yīng)熱冷卻解決方案。我們也測(cè)試?yán)匣K羞@些對(duì)于設(shè)備在現(xiàn)場(chǎng)能使用多長(zhǎng)時(shí)間以及我們攜帶它們多長(zhǎng)時(shí)間至關(guān)重要。因此,我們?nèi)杂锌蛻糍?gòu)買Virtex-5芯片(于2006年推出)。而在汽車領(lǐng)域,您可能需要覆蓋20到25年。

可見(jiàn)的篡改

篡改始終是硬件和軟件關(guān)注的問(wèn)題。標(biāo)準(zhǔn)FPGA已提交并驗(yàn)證了其硬件。無(wú)論它是否具有固有的安全性,攻擊者都將無(wú)法篡改該基本硬件。但是,仍然可以通過(guò)弄亂比特流并更改加載的圖像來(lái)篡改結(jié)構(gòu)的內(nèi)容。

幾年前,柏林理工大學(xué)的一組研究人員使用非接觸式探測(cè)技術(shù)提出了一篇論文,表明這是可能的。

“除了產(chǎn)生電信號(hào)外,這些晶體管還發(fā)射少量的紅外光,它們還將調(diào)制紅外信號(hào),具體取決于晶體管通道是處于活動(dòng)狀態(tài)還是處于活動(dòng)狀態(tài)”,防偽產(chǎn)品技術(shù)總監(jiān)Scott Best說(shuō)。Rambus。“因此,使用非常精確的紅外激光,您可以將激光從晶體管反射回來(lái),然后回來(lái),它將告訴您該晶體管是打開(kāi)還是關(guān)閉,以及那里是否有電壓。您可以將感應(yīng)與晶體管切換或信號(hào)在總線上轉(zhuǎn)換的時(shí)間同步。為此需要做一些材料準(zhǔn)備工作,因?yàn)橥ǔJ褂萌魏胃叻直媛剩夹枰獙⑿酒趁娴暮穸葟?50微米減薄到25微米。因此,現(xiàn)在紅外線很容易從硅片的背面逸出,您將獲得真正的高分辨率以檢測(cè)紅外線的發(fā)射。”

借助eFPGA,該陣列以軟形式實(shí)例化,因此流氓設(shè)計(jì)人員可以在將設(shè)計(jì)投入硅之前對(duì)其進(jìn)行篡改。但是,由于織物的排列特性,如果在目視檢查中看不到這種變化,則很難進(jìn)行改變。在門相對(duì)混亂的設(shè)計(jì)中調(diào)整某些東西要容易得多,在這種情況下,變化很難被發(fā)現(xiàn)。“當(dāng)您擁有嵌入式FPGA或存儲(chǔ)器之類的陣列結(jié)構(gòu)時(shí),很難在其中放置特洛伊木馬電路而不干擾統(tǒng)一的陣列結(jié)構(gòu),” Tate說(shuō)道。

另外,eFPGA的一些關(guān)鍵用戶需要其他方法來(lái)檢測(cè)可能的篡改。例如,可以模擬典型工作負(fù)載下芯片的預(yù)期功率曲線,然后在構(gòu)建時(shí)將其與實(shí)際芯片進(jìn)行比較。如果它們之間的差異太大,則表明存在某些問(wèn)題。再次強(qiáng)調(diào),防止篡改并不僅僅是使篡改的任何嘗試更加明顯。

eFPGA比特流的詳細(xì)信息通常不會(huì)在數(shù)據(jù)表和應(yīng)用筆記中發(fā)布。通常,只有NDA下的重要客戶才能使用它們,并且提供eFPGA的公司可能會(huì)拒絕與動(dòng)機(jī)不佳的人合作。這不是對(duì)比特流內(nèi)容的嚴(yán)格保護(hù),但確實(shí)提供了另一層保護(hù)。

雖然標(biāo)準(zhǔn)的FPGA帶有一個(gè)保存其內(nèi)容的存儲(chǔ)器,但是eFPGA通常使用引導(dǎo)ROM進(jìn)行存儲(chǔ)。當(dāng)然,標(biāo)準(zhǔn)的FPGA也可以做到這一點(diǎn),但是位流塊將以FPGA制造商確定的格式存儲(chǔ)。使用嵌入式FPGA,設(shè)計(jì)人員可以自由控制位流在內(nèi)存中的位置,并且通常比引導(dǎo)代碼本身小得多。堅(jiān)定的設(shè)計(jì)工程師甚至可以對(duì)比特流進(jìn)行加擾,以便將其散布在存儲(chǔ)器的不同部分中,而不是散布在一個(gè)塊中。

防止比特流被篡改的另一種方法是對(duì)存儲(chǔ)中的比特流進(jìn)行加密,僅在將其加載到設(shè)備中時(shí)解密。在現(xiàn)成的FPGA中,任何這種加密都將在銷售FPGA的公司的控制下進(jìn)行。使用eFPGA,特定的加密技術(shù)和保護(hù)密鑰的方法仍在設(shè)計(jì)者的控制之下。

Tate說(shuō):“客戶無(wú)需告訴我們他們?nèi)绾螌FPGA配置代碼映射到其閃存中。” “他們可以加密部分或全部閃存,并在SoC中解密。他們可以分條或使用其他算法“散列”地址以非線性方式進(jìn)行存儲(chǔ)。或者他們可以兩者都做。”

禁用JTAG端口

對(duì)于基于處理器和基于FPGA的系統(tǒng),仍然存在一種臭名昭著的爬入系統(tǒng)的方法-JTAG(或其他調(diào)試)端口。通過(guò)此端口可以訪問(wèn)內(nèi)部邏輯的廣闊區(qū)域。盡管內(nèi)部掃描鏈的組織對(duì)于逆向工程可能很繁瑣,但這并非不可能。

因此,在安全性尤為重要的情況下,設(shè)計(jì)通常會(huì)在設(shè)計(jì)和制造完成后禁用JTAG端口。有時(shí)這是通過(guò)不可逆轉(zhuǎn)地熔斷保險(xiǎn)絲來(lái)實(shí)現(xiàn)的。如果使用此選項(xiàng),則將來(lái)將無(wú)法使用JTAG端口來(lái)幫助診斷任何問(wèn)題。

另一種選擇是通過(guò)位流禁用JTAG端口。最終映像可以包含有關(guān)禁用JTAG端口的說(shuō)明。如果將來(lái)需要退回設(shè)備進(jìn)行故障分析,則創(chuàng)建比特流的公司可以加載專用比特流,該專用比特流僅使JTAG端口僅供內(nèi)部使用。

也可以用密碼保護(hù)JTAG,盡管這帶來(lái)了管理密鑰的挑戰(zhàn)。將單個(gè)密鑰用于所有設(shè)備嗎?然后入侵一臺(tái)設(shè)備將解鎖其他所有設(shè)備。但是,現(xiàn)在為每臺(tái)設(shè)備使用不同的密鑰給配置功能帶來(lái)了挑戰(zhàn),因?yàn)樵摴δ懿惶赡芙?jīng)常使用。因此,這可能是實(shí)施起來(lái)比較困難的選擇。

所有這些考慮因素還受到構(gòu)建FPGA的技術(shù)的影響。到目前為止,目前使用的大多數(shù)FPGA使用SRAM內(nèi)容,這些內(nèi)容必須在上電時(shí)重新加載。這是位流管理最重要的地方。例如,對(duì)于重新加載啟用JTAG端口的比特流,它也更加靈活。

基于閃存的設(shè)備中的非易失性配置消除了每次上電時(shí)加載比特流的需要。設(shè)備是在制造過(guò)程中配置的,因此一旦設(shè)備部署,攻擊者就很難更改其內(nèi)容。話雖如此,Oberg指出,基于SRAM的設(shè)備可以在必要時(shí)使用冗余,以抵御單事件干擾和內(nèi)容更改—假設(shè)任何篡改僅發(fā)生在冗余集之一上。

多租戶–處理器和FPGA

數(shù)據(jù)中心提出了另一種安全挑戰(zhàn)–多租戶。對(duì)于處理器,其想法是多個(gè)客戶端可以使用一臺(tái)服務(wù)器。由服務(wù)器基礎(chǔ)結(jié)構(gòu)來(lái)確保來(lái)自一個(gè)客戶端的信息不會(huì)泄漏到另一客戶端。這可以通過(guò)分離內(nèi)存和分時(shí)處理器本身來(lái)完成。

也有興趣為數(shù)據(jù)中心中的FPGA加速器提供多租戶訪問(wèn)。Hallman說(shuō):“分區(qū)對(duì)于保持一定程度的隔離非常重要。” 與其分時(shí)共享處理器,不如共享一個(gè)FPGA結(jié)構(gòu)空間,其中一部分包含一個(gè)客戶端使用的邏輯,另一部分包含另一客戶端的邏輯。

當(dāng)然,這比共享處理器要復(fù)雜得多。如何管理不同的圖像?即使在運(yùn)行時(shí),它們是否可以獨(dú)立于邏輯的其他客戶端部分進(jìn)行加載或重新配置?如何在兩個(gè)客戶端之間隔離硬件?Hallman說(shuō):“我進(jìn)行了一些特定的對(duì)話,客戶希望允許訪問(wèn)FPGA設(shè)計(jì)的某些部分,但他們希望鎖定其他部分,尤其是在數(shù)據(jù)中心應(yīng)用程序中。”

能夠進(jìn)行這種劃分的硬件元件將是部分重編程電路。這定義了可以重新編程FPGA架構(gòu)而無(wú)需接觸FPGA其他部分的粒度。但是除此之外,域之間的信號(hào)交叉沒(méi)有物理障礙。Hallman表示,必須通過(guò)驗(yàn)證獨(dú)立域互不影響來(lái)通過(guò)驗(yàn)證來(lái)實(shí)施分區(qū)。

盡管這是一個(gè)有趣的場(chǎng)景,但它可能不如基于處理器的多租戶的隔離技術(shù)那么完善。而且,由于它是硬件而不是軟件,因此使其成為安全啟用的難度更大。目前,這并不常見(jiàn)。泰特說(shuō):“大多數(shù)客戶在運(yùn)營(yíng)期間不會(huì)即時(shí)進(jìn)行編程。”

結(jié)論

在處理器和FPGA上的軟件中實(shí)現(xiàn)功能之間的選擇涉及經(jīng)典的權(quán)衡。軟件更靈活,更易于更改。FPGA比強(qiáng)化邏輯更靈活,但仍不如軟件靈活。安全成為此決定中的另一個(gè)考慮因素。如果需要最終的安全性,則FPGA和嵌入式FPGA可以使系統(tǒng)比軟件更安全。

但這不是萬(wàn)能藥。“與傳統(tǒng)的軟件/微處理器相比,F(xiàn)PGA實(shí)施面臨許多相同的挑戰(zhàn),例如加密閃存,安全啟動(dòng)以及免受系統(tǒng)內(nèi)攻擊的保護(hù),” Mallett說(shuō)。盡管有機(jī)會(huì)獲得更好的安全性,但仍有大量工作要做。

責(zé)任編輯:tzh

-

處理器

+關(guān)注

關(guān)注

68文章

20255瀏覽量

252271 -

FPGA

+關(guān)注

關(guān)注

1660文章

22412瀏覽量

636303 -

芯片

+關(guān)注

關(guān)注

463文章

54010瀏覽量

466045 -

soc

+關(guān)注

關(guān)注

40文章

4576瀏覽量

229140

發(fā)布評(píng)論請(qǐng)先 登錄

探索TDA54x Jacinto?處理器:高性能與安全的完美融合

MAX6323/MAX6324:微處理器監(jiān)控電路的卓越之選

ADM8323/ADM8324:微處理器系統(tǒng)的可靠監(jiān)控伙伴

MAX1232微處理器監(jiān)控器:高效可靠的系統(tǒng)守護(hù)專家

如何使用Lopper實(shí)用工具為目標(biāo)處理器生成DTB

Cortex-M0 處理器介紹

S32Z2:安全可靠的高性能實(shí)時(shí)處理器

AMD推出 EPYC 嵌入式 2005 系列處理器 滿足長(zhǎng)期部署需求

嵌入式和FPGA的區(qū)別

在物聯(lián)網(wǎng)設(shè)備面臨的多種安全威脅中,數(shù)據(jù)傳輸安全威脅和設(shè)備身份安全威脅有何本質(zhì)區(qū)別?

云拼接處理器的性能如何?

請(qǐng)問(wèn)NICE協(xié)處理器與傳統(tǒng)ocb外設(shè)相比的優(yōu)勢(shì)有什么?

NICE協(xié)處理器與傳統(tǒng)ocb外設(shè)相比的優(yōu)勢(shì)有什么?

MAX32590 DeepCover安全微處理器,集成ARM926EJ-S處理器核技術(shù)手冊(cè)

DS5003安全微處理器芯片技術(shù)手冊(cè)

FPGA系統(tǒng)中的安全性相比處理器有區(qū)別嗎

FPGA系統(tǒng)中的安全性相比處理器有區(qū)別嗎

評(píng)論