本案例來源于第三屆全國大學生FPGA創(chuàng)新設計競賽中江南大學的OpenHEC lab團隊,他們的作品基于PYNQ開源軟件框架。PYNQ框架提供了完整的訪問FPGA資源的Python library,通過高層次的封裝,讓開發(fā)者通過Python API就可以輕松調用FPGA內的模塊或算法,加速產(chǎn)品開發(fā)部署。

由于篇幅有限,我們將其作品分為兩期進行介紹。這期我們主要介紹本作品的設計概述 和最終能達到的效果,下一期將會向大家展示作品詳細的加速設計。有關作品的資料可以在參考文獻中的GitHub鏈接自行下載。

第一部分 設計概述

1.1、設計目的

- 通過基于SNN的類腦計算方式更好地解決無監(jiān)督的圖像識別問題通過軟硬件協(xié)同的方式更好地探索大規(guī)模、低功耗類腦系統(tǒng)的設計空間

- 通過開源開放推動更多人開展基于FPGA的類腦體系結構研究與學習[1]。

1.2、技術特點

- 提供基于脈沖神經(jīng)網(wǎng)絡的圖像識別的解決方案;

- 支持開源類腦計算仿真框架PYNN[2]、脈沖神經(jīng)網(wǎng)絡仿真器NEST[3];

- 提供基于類腦計算的神經(jīng)元模塊硬件加速和突觸模塊硬件加速模塊;

- 支持PYNQ集群,采用MPI多進程和OpenMP多線程設計。

第二部分 系統(tǒng)組成及功能說明

2.1、基于脈沖網(wǎng)絡的皮質層視覺仿真模型介紹

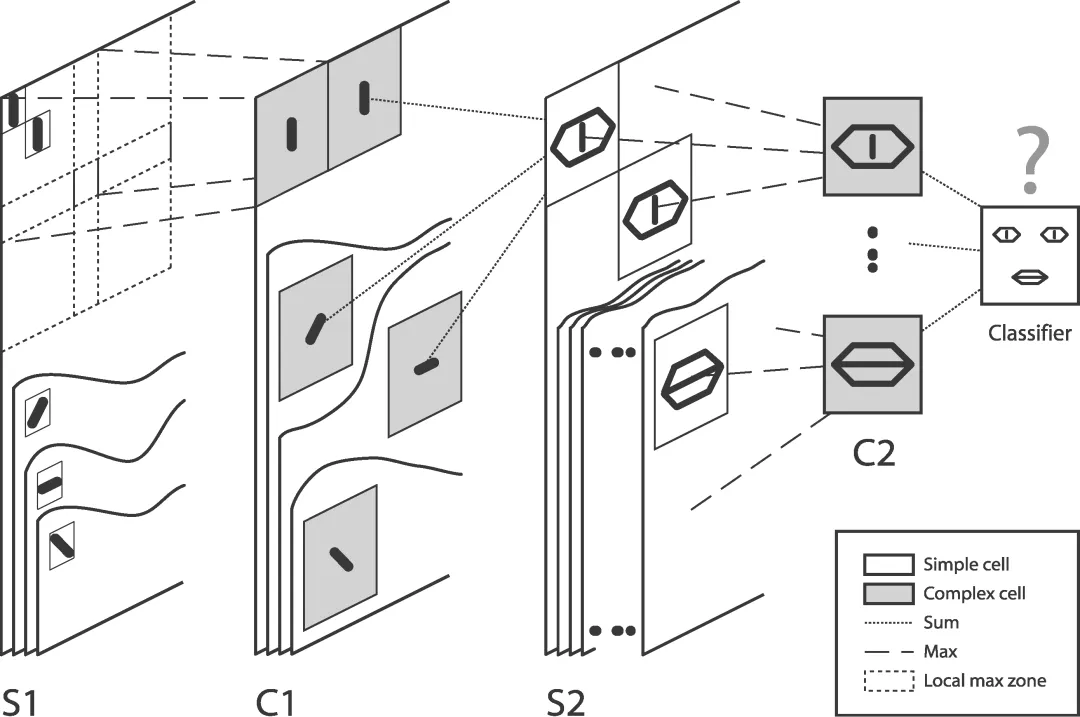

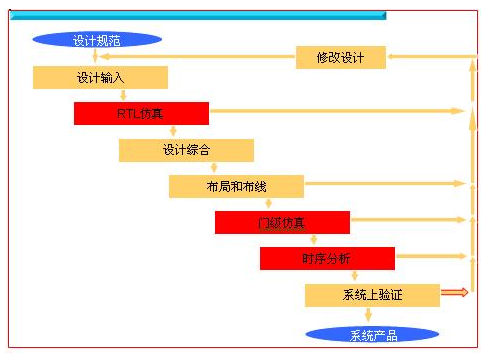

基于脈沖神經(jīng)網(wǎng)絡的皮質層視覺仿真模型由5層尖峰神經(jīng)元組成。層與層之間以脈沖的方式進行信息傳遞,C1-S2層之間采用STDP(Spike-Timing-Dependent Plasticity)算法對對象特征進行學習。該網(wǎng)絡架構屬于麻省理工學院Riesenhuber&Poggio提出的HMAX模型中的一種[5][6],通過模擬哺乳動物腦皮層視覺,實現(xiàn)對圖像識別的功能,如圖1所示。

2.2、基于PYNQ集群的類腦計算平臺介紹

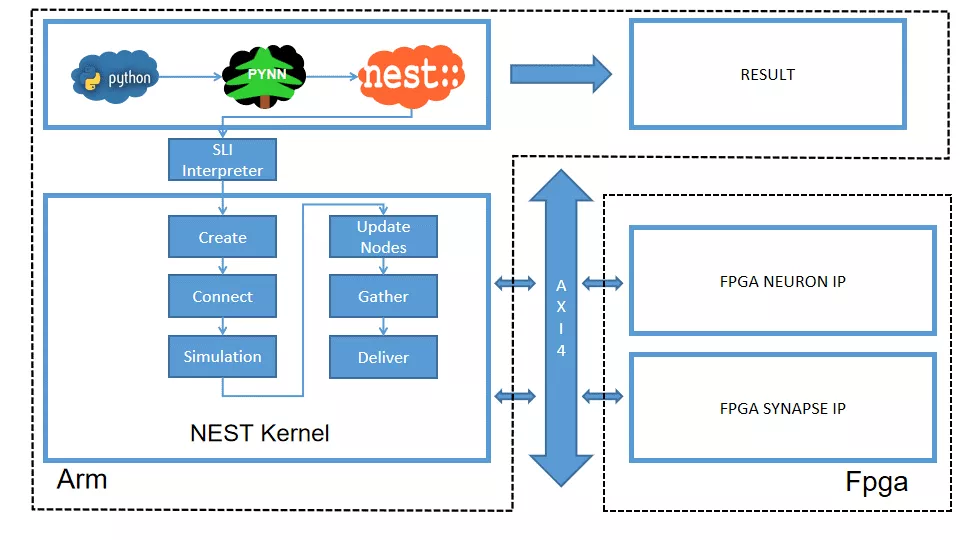

本系統(tǒng)由包含PYNN類腦框架、NEST仿真器、FPGA神經(jīng)元和STDP硬件模塊。如圖2所示,頂層應用設計語言為Python,在PYNN架構協(xié)助下調用NEST仿真器,各種命令通過python interpreter和SLI interpreter解釋后,進入NEST kernel。根據(jù)各種命令進行底層網(wǎng)絡創(chuàng)建包括神經(jīng)元創(chuàng)建、突觸連接創(chuàng)建、仿真時間設置等。

在此基礎上,本組設計了FPGA神經(jīng)元加速模塊和FPGA STDP突觸加速模塊,根據(jù)不網(wǎng)絡拓撲和計算要求,為不同計算密集點提供加速模塊。

圖2 類腦計算平臺整體框架

2.3、通用的類腦仿真實驗平臺

如圖3所示,本課題的通用平臺集成8塊PYNQ板,板級連接遵循TCP/IP協(xié)議。PYNQ-Z2 開發(fā)板以 ZYNQ XC7Z020 FPGA為核心,配備有以太網(wǎng),HDMI輸入/輸出,MIC輸入,音頻輸出,Arduino 接口,樹莓派接口,2 個 Pmod,用戶 LED,按鈕和開關。

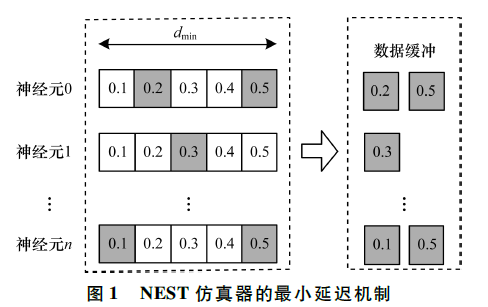

2.4、NEST系統(tǒng)介紹

NEST作為一款非常流行的類腦模擬器開源軟件,應用廣泛。NEST一大優(yōu)勢是可用于模擬任何規(guī)模的脈沖神經(jīng)網(wǎng)絡,如可模擬哺乳動物的視覺或聽覺皮層這樣的信息處理模型。也可模擬網(wǎng)絡活動的動力學模型,比如層狀皮質網(wǎng)絡或平衡隨機網(wǎng)絡以及學習和可塑性模型。同時NEST的另一大優(yōu)勢就是支持集成式的MPI、OpenMP通訊協(xié)議,可以進行分布式計算大大提高仿真速度。

如圖2所示,NEST的主體結構分為創(chuàng)建模型、連接模型,模擬仿真。仿真模塊分為突觸傳遞、更新神經(jīng)元、MPI傳輸。針對對應用計算密集點分析,本設計主要是對于更新神經(jīng)元模塊和突觸模塊進行加速。

第三部分 完成情況及性能參數(shù)

3.1、軟硬件環(huán)境介紹

- NEST仿真器: NEST 2.14.0版本。

- 皮質層視覺仿真模型:最小延遲為1ms,仿真精度為0.1ms,總生物仿真時間為50ms,神經(jīng)元數(shù)量為48904,突觸數(shù)量為275456。

- FPGA設計軟件:Xilinx Vivado 2018、Xilinx Vivado HLS 2018。

- CPU:Inter Xenon E5-2620,其內存為128GB DDR3。

- FPGA集群系統(tǒng):FPGA集群包含8個Xilinx PYNQ節(jié)點,每個節(jié)點包括PS(Process System)端的ARM A9雙核處理器系統(tǒng)和一個PL(可編程邏輯)端的FPGA器件。FPGA時鐘頻率為100MHZ。FPGA板卡之間采用1000Mbps網(wǎng)絡帶寬的以太網(wǎng)進行通信,并采用TCP/IP協(xié)議。

3.2、皮質層視覺模型仿真結果

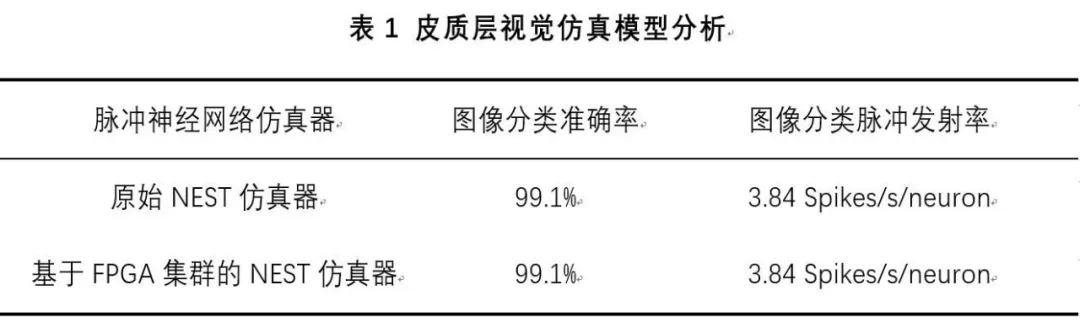

本文NEST仿真器中神經(jīng)元計算模塊采用單精度浮點數(shù)據(jù)精度,與原NEST仿真器的神經(jīng)元計算模塊雙精度浮點數(shù)據(jù)精度相比,在皮質層視覺模型仿真圖像分類的準確率和脈沖發(fā)射率方面并無差別,其結果如表1所示。

3.3、性能評估

本文實現(xiàn)基于FPGA集群的脈沖神經(jīng)網(wǎng)絡仿真器NEST,以皮質層視覺模型仿真為案例,分別對比Inter服務器版CPU Xenon E5-2620和ARM A9雙核CPU,其時鐘頻率、內存、性能等,如表2所示:

本文中實現(xiàn)的基于FPGA集群的NEST仿真器,在計算能效方面,其單個節(jié)點能效是ARM A9的30倍,是Inter Xeon E5-2620的56.10倍;FPGA集群的能效是Inter Xeon E5-2620的43.93倍,是ARM A9的23.54倍。在速度方面,單個節(jié)點速度是ARM A9的33.21倍,是Inter Xeon E5-2620的1.97倍;FPGA集群的速度是ARM A9的208倍,是Inter Xeon E5-2620的12.36倍。

參考文獻

1. https://github.com/OpenHEC/SNN-simulator-on-PYNQcluster.

2. http://neuralensemble.org/PyNN/.

3. https://www.nest-simulator.org/.

4. Masquelier, Timothée, Thorpe S J. Unsupervised Learning of Visual Features through Spike Timing Dependent Plasticity[J].PLoS Computational Biology, 2007, 3(2):e31.

5. Serre T, Wolf L, Poggio T (2005) Object recognition with features inspired by visual cortex. CVPR 2: 994–1000.

6. Riesenhuber M, Poggio T (1999) Hierarchical models of object recognition in cortex. Nat Neurosci 2: 1019–1025.

-

FPGA

+關注

關注

1660文章

22415瀏覽量

636540 -

仿真器

+關注

關注

14文章

1051瀏覽量

87340 -

圖像識別

+關注

關注

9文章

534瀏覽量

40069 -

Nest

+關注

關注

1文章

47瀏覽量

17082

發(fā)布評論請先 登錄

基于FPGA的類腦計算平臺 —PYNQ 集群的無監(jiān)督圖像識別類腦計算系統(tǒng)

基于VC的飛行仿真器導航仿真系統(tǒng)開發(fā)

Ansoft仿真器

什么是單片機仿真器_單片機仿真器有什么用_單片機仿真器怎么用

米爾科技ULINKpro D 仿真器介紹

ModelSim仿真器的主要特點以及用法解析

基于FPGA集群的NEST脈沖神經(jīng)網(wǎng)絡仿真器

ADI公司基于USB的仿真器和基于USB的高性能仿真器產(chǎn)品亮點

STM32-DAP仿真器的使用(1)

仿真器是什么?語音芯片的仿真器有幾種?

基于FPGA集群的NEST仿真器設計

基于FPGA集群的NEST仿真器設計

評論