存儲體系結構有哪些

1、低端存儲

一般只有一個控制器,基本沒有cache或者有很少的cache,所以整體響應速度慢,而且基本沒有冗余,可靠性差,一般適用于可靠性要求不高的應用,或者用來做備份。

2、中端存儲

一般采用雙控,有較多的cache或鏈路,而且開始注意冗余,這個區間的存儲,控制器是核心部分,如果有1個控制器壞掉,帶來的性能降低會超過50%,因為損壞一個控制器后寫cache會自動關閉,性能受到極大影響。

3、高端存儲

一般采用多控,并采用以cache為核心的體系結構。多控的結構中,損壞其中某個控制器對整體性能影響比較小。

一般情況下,中端存儲是性價比較高的可選產品,對于可靠性及響應要求極高的應用,會采用高端存儲,比如銀行、電信、移動等。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

控制器

+關注

關注

114文章

17797瀏覽量

193397 -

存儲

+關注

關注

13文章

4797瀏覽量

90079

發布評論請先 登錄

相關推薦

熱點推薦

低功耗同步SRAM擴展存儲器結構特點

,都能見到它的身影。在計算機體系結構中,同步SRAM主要用于實現CPU內部的高速緩存,包括一級緩存(L1 Cache)和二級緩存(L2 Cache)。對于需要高速數據處理的系統,SRAM也常以突發模式緩存的形式存在,有效橋接處理器與主存之間的速度差異。

操作系統體系結構

問題是性能問題,因為需要頻繁地在核心態和用戶態之間進行切換,操作系統的執行開銷偏大。因此有的操作系統將那些頻繁使用的系統服務又移回內核,從而保證系統性能。但是有相當多的實驗數據表明,體系結構不是引起性能下降

發表于 01-15 08:19

芯盾時代助力長江存儲構建全場景身份安全體系

芯盾時代中標長江存儲,基于零信任安全理念,通過自研的用戶身份與訪問管理平臺(IAM),結合半導體行業業務場景特點,為長江存儲構建全場景、高安全、智能化的身份安全體系,實現用戶全生命周期管理,有效防范身份安全帶來的經濟損失,助力其

stt-marm存儲芯片的結構原理

在存儲技術快速演進的今天,一種名為STT-MRAM(自旋轉移矩磁阻隨機存取存儲器)的新型非易失存儲器,正逐步走入產業視野。它不僅繼承了MRAM的高速讀寫能力與非易失特性,更通過“自旋電流”技術實現了信息寫入方式的突破,被視為第二

DSP的基礎

;

④特殊的體系結構,適合于運算密集的應用場合;

⑤內部硬件乘法器,乘法運算時間短、速度快;

⑥高度的集成性,帶有多種存儲器接口和IO互聯接口;

⑦普遍帶有DMA通道控制器,保證數據傳輸和計算處理并行

發表于 11-20 06:35

MD5信息摘要算法實現二(基于蜂鳥E203協處理器)

處理器的運算結果通過返回電路將數據存儲在對應的地址中,這里的地址即串口程序助手進行取指的地方。NICE接口和MD5協處理器SoC體系結構設計圖如下圖3-10所示。

圖1 NICE接口和MD5協

發表于 10-30 07:54

恩智浦i.MX RT1180 MCU如何進入Boundary Scan模式

本文重點介紹RT1180如何進入Boundary Scan模式,通過Jtag來進行板級硬件測試的過程。遵循IEEE1149.1中的測試訪問端口和BoundaryScan體系結構的標準。

DPU核心技術論文再次登陸體系結構領域旗艦期刊《IEEE Transactions on Computers》

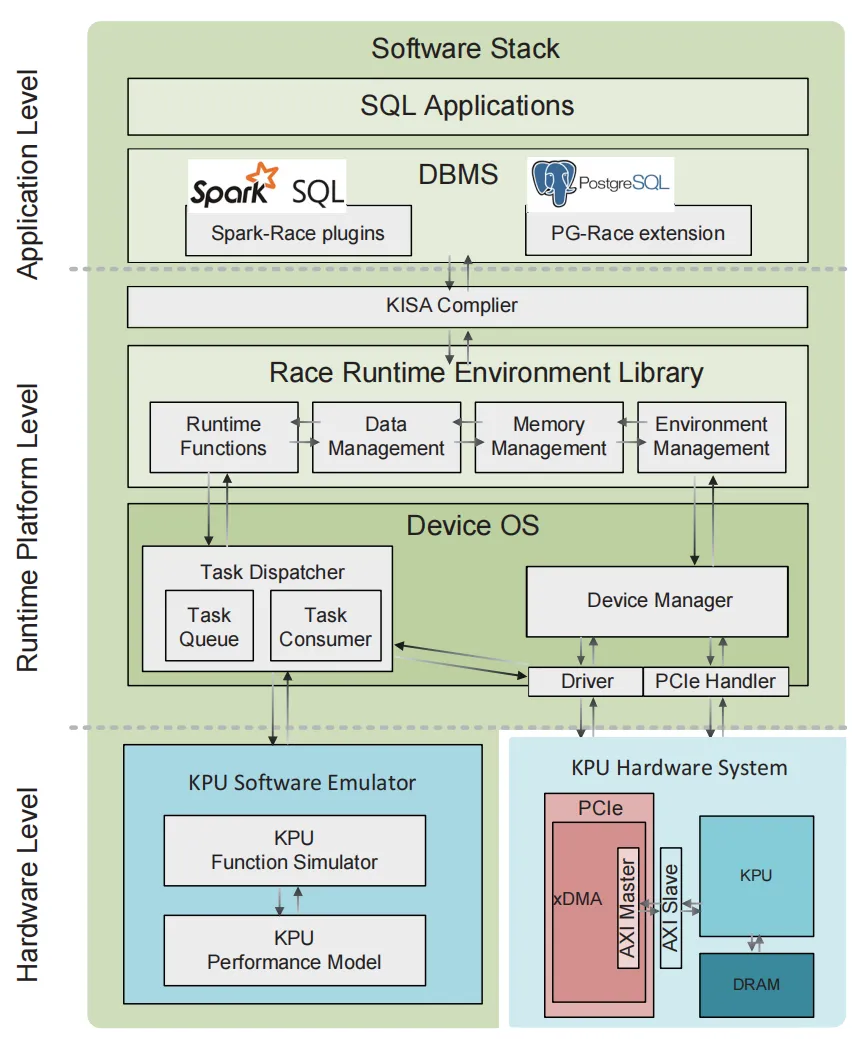

近期,鄢貴海團隊研究成果在計算機體系結構領域國際頂級期刊《IEEE Transactions on Computers》中發表。該研究主要圍繞KPU敏捷計算架構展開,KPU具有超強異構核集成和調度

存儲示波器的存儲深度對信號分析有什么影響?

存儲深度(Memory Depth)是數字示波器的核心參數之一,它直接決定了示波器在單次采集過程中能夠記錄的采樣點數量。存儲深度對信號分析的影響貫穿時域細節捕捉、頻域分析精度、觸發穩定性等多個維度

發表于 05-27 14:39

睿創微納AI芯片技術登上國際計算機體系結構領域頂級會議

近日,國際計算機體系結構領域頂級會議HPCA 2025(International Symposium on High-Performance Computer Architecture)在美國召開。會議共收到534篇來自全球頂尖科研機構及高校的論文投稿,最終錄用率僅為21%。

MCU存儲器層次結構解析

? ? ? ?MCU的存儲器層次結構通過整合不同性能與功能的存儲單元,優化系統效率并滿足多樣化場景需求。其核心架構可分為以下層次: 一、寄存器層(最高速) 定位?:集成于CPU內核中,直接參與運算

嵌入式硬件基礎知識匯總(附帶與硬件密切相關的軟件介紹)

和多元的特征與要求。兩種典型存儲體系:

1,以CPU為核心的、片內和片外存儲資源相融合的存儲體系;

2,與通用計算機相似的

發表于 03-26 11:12

存儲體系結構有哪些

存儲體系結構有哪些

評論